F28377D的W5300例程如何在CPU2中运行

想要让W5300的例程在F28377D的CPU2中运行,应该如何设置,具体如何配置CPU1和CPU2?用的是研

想要让W5300的例程在F28377D的CPU2中运行,应该如何设置,具体如何配置CPU1和CPU2?用的是研

问一下关于TI的DSP的地址线或数据线,是否可以既当地址线用,又当数据线用的做法?我目前在准备的是TMS320

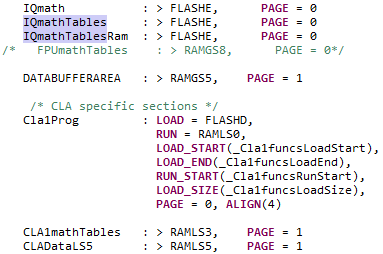

将程序烧录到片上FLASH的cmd配置代码中的部分如下:1、此处将IQmath、IQmathTables、IQ

基于28377的cmd文件中已经有如下配置: #ifdef CLA_C /* CLA C compiler s

本人设置了CLA协处理器及又CLA协处理器末尾给定EPwm3Regs.CMPA.bit.CMPA = EPwm

28377上CLA协处理器可以直接通过EMIF写数据到外部FPGA吗?有没有其它方法可以实现?Eric Ma:

本人在TI例程cla_adc_fir32_cpu01中添加TIMER0中断,增加中断处理的内容,在各个中断进入时拉高相应的管脚电平,在各自处理完内容后又都拉低相应的管脚电平,在测试中发现两个中断相互产生了影响,并不是像手册所说的CLA协处理...