hi,各位专家

大家好,如题遇到ECAN调试出错的问题。

总线上还有一个其他公司的CAN收发器。

现有A板ECAN和B板ECAN,若增加挂载A或B板的ECAN都能够正常收发,通时增加挂载两个ECAN时,假设A板正常,B板总是会出错!

下载到A板和B板的程序只有发送邮箱不同,其它配置一样。就算是A、B板的程序换过来烧写,还是B板出错。

请问这可能是什么原因呢??急急急!!

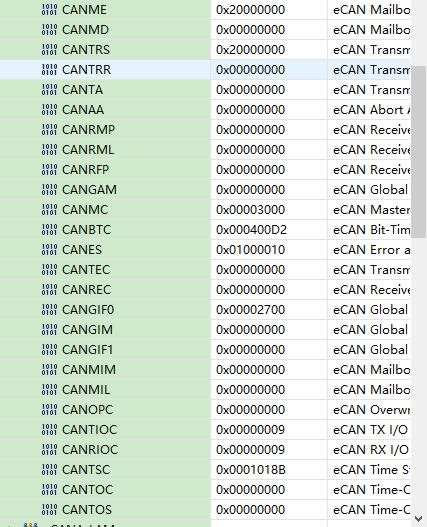

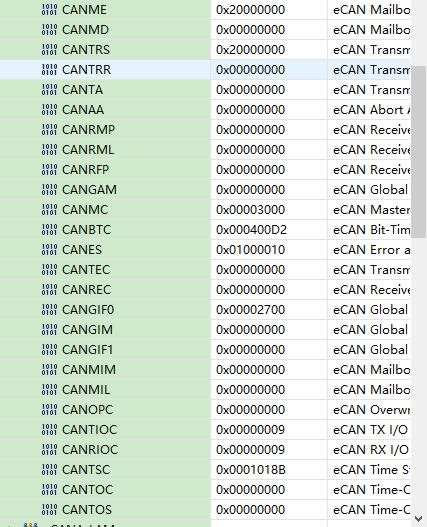

下面附上错误时的寄存器状态和初始化配置程序。

谢谢!!

void InitECana(void) // Initialize eCAN-A module

{

/* Create a shadow register structure for the CAN control registers. This is

needed, since only 32-bit access is allowed to these registers. 16-bit access

to these registers could potentially corrupt the register contents or return

false data. This is especially true while writing to/reading from a bit

(or group of bits) among bits 16 – 31 */

struct ECAN_REGS ECanaShadow;

EALLOW; // EALLOW enables access to protected bits

/* Configure eCAN RX and TX pins for CAN operation using eCAN regs*/

ECanaShadow.CANTIOC.all = ECanaRegs.CANTIOC.all;

ECanaShadow.CANTIOC.bit.TXFUNC = 1;

ECanaRegs.CANTIOC.all = ECanaShadow.CANTIOC.all;

ECanaShadow.CANRIOC.all = ECanaRegs.CANRIOC.all;

ECanaShadow.CANRIOC.bit.RXFUNC = 1;

ECanaRegs.CANRIOC.all = ECanaShadow.CANRIOC.all;

/* Configure eCAN for HECC mode – (reqd to access mailboxes 16 thru 31) */

// HECC mode also enables time-stamping feature

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.SCB = 1;

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

/* Initialize all bits of 'Master Control Field' to zero */

// Some bits of MSGCTRL register come up in an unknown state. For proper operation,

// all bits (including reserved bits) of MSGCTRL must be initialized to zero

ECanaMboxes.MBOX0.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX1.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX2.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX3.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX4.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX5.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX6.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX7.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX8.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX9.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX10.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX11.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX12.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX13.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX14.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX15.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX16.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX17.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX18.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX19.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX20.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX21.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX22.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX23.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX24.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX25.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX26.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX27.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX28.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX29.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX30.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX31.MSGCTRL.all = 0x00000000;

// TAn, RMPn, GIFn bits are all zero upon reset and are cleared again

// as a matter of precaution.

ECanaRegs.CANTA.all = 0xFFFFFFFF; /* Clear all TAn bits */

ECanaRegs.CANRMP.all = 0xFFFFFFFF; /* Clear all RMPn bits */

ECanaRegs.CANGIF0.all = 0xFFFFFFFF; /* Clear all interrupt flag bits */

ECanaRegs.CANGIF1.all = 0xFFFFFFFF;

/* Configure bit timing parameters for eCANA*/

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.CCR = 1 ; // Set CCR = 1

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

do

{

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

} while(ECanaShadow.CANES.bit.CCE != 1 ); // Wait for CCE bit to be set..

ECanaShadow.CANBTC.all = 0;

#if (CPU_FRQ_150MHZ) // CPU_FRQ_150MHz is defined in DSP2833x_Examples.h

/* The following block for all 150 MHz SYSCLKOUT (75 MHz CAN clock) – default. Bit rate = 1 Mbps

See Note at End of File */

ECanaShadow.CANBTC.bit.BRPREG = 4;

ECanaShadow.CANBTC.bit.TSEG2REG = 2;

ECanaShadow.CANBTC.bit.TSEG1REG = 10;

#endif

#if (CPU_FRQ_100MHZ) // CPU_FRQ_100MHz is defined in DSP2833x_Examples.h

/* The following block is only for 100 MHz SYSCLKOUT (50 MHz CAN clock). Bit rate = 1 Mbps

See Note at End of File */

ECanaShadow.CANBTC.bit.BRPREG = 4;

ECanaShadow.CANBTC.bit.TSEG2REG = 1;

ECanaShadow.CANBTC.bit.TSEG1REG = 6;

#endif

ECanaShadow.CANBTC.bit.SAM = 1;

ECanaRegs.CANBTC.all = ECanaShadow.CANBTC.all;

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.CCR = 0 ; // Set CCR = 0

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

do

{

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

} while(ECanaShadow.CANES.bit.CCE != 0 ); // Wait for CCE bit to be cleared..

/* Disable all Mailboxes */

ECanaRegs.CANME.all = 0; // Required before writing the MSGIDs

EDIS;

//——————————————————————————————–

// Mailboxs can be written to 16-bits or 32-bits at a time

// ECanaMboxes.MBOX30.MSGID.all = 0x90000030; //Sent out

ECanaMboxes.MBOX29.MSGID.all = 0x01fffff29;

// ECanaMboxes.MBOX31.MSGID.all = 0x90000031; //Receive

// Configure Mailboxes 30/29 as Tx—0, 31 as Rx—-1

// Since this write is to the entire register (instead of a bit

// field) a shadow register is not required.

ECanaRegs.CANMD.all = 0x00000000;

// Enable 30/31 Mailboxes */

// Since this write is to the entire register (instead of a bit

// field) a shadow register is not required.

// ECanaRegs.CANME.all = 0xF0000000;

ECanaRegs.CANME.all = 0x20000000; //31 30 29 28 0010

// ECanaRegs.CANME.all = 0x40000000; //31 30 29 28 0100

// Specify that 8 bits will be sent/received

// ECanaMboxes.MBOX30.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX29.MSGCTRL.bit.DLC = 8;

// ECanaMboxes.MBOX30.MSGCTRL.bit.DLC = 8;

// ECanaMboxes.MBOX31.MSGCTRL.bit.DLC = 8;

}

Johnson Chen1:

从现象看的话,应该是硬件的问题。A 板和B 板是C2000是一个型号吗?通讯速度是多高?有没有可能是波特率误差导致?另外120Ohm的匹配电阻A和B两个板子都有吗?

hi,各位专家

大家好,如题遇到ECAN调试出错的问题。

总线上还有一个其他公司的CAN收发器。

现有A板ECAN和B板ECAN,若增加挂载A或B板的ECAN都能够正常收发,通时增加挂载两个ECAN时,假设A板正常,B板总是会出错!

下载到A板和B板的程序只有发送邮箱不同,其它配置一样。就算是A、B板的程序换过来烧写,还是B板出错。

请问这可能是什么原因呢??急急急!!

下面附上错误时的寄存器状态和初始化配置程序。

谢谢!!

void InitECana(void) // Initialize eCAN-A module

{

/* Create a shadow register structure for the CAN control registers. This is

needed, since only 32-bit access is allowed to these registers. 16-bit access

to these registers could potentially corrupt the register contents or return

false data. This is especially true while writing to/reading from a bit

(or group of bits) among bits 16 – 31 */

struct ECAN_REGS ECanaShadow;

EALLOW; // EALLOW enables access to protected bits

/* Configure eCAN RX and TX pins for CAN operation using eCAN regs*/

ECanaShadow.CANTIOC.all = ECanaRegs.CANTIOC.all;

ECanaShadow.CANTIOC.bit.TXFUNC = 1;

ECanaRegs.CANTIOC.all = ECanaShadow.CANTIOC.all;

ECanaShadow.CANRIOC.all = ECanaRegs.CANRIOC.all;

ECanaShadow.CANRIOC.bit.RXFUNC = 1;

ECanaRegs.CANRIOC.all = ECanaShadow.CANRIOC.all;

/* Configure eCAN for HECC mode – (reqd to access mailboxes 16 thru 31) */

// HECC mode also enables time-stamping feature

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.SCB = 1;

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

/* Initialize all bits of 'Master Control Field' to zero */

// Some bits of MSGCTRL register come up in an unknown state. For proper operation,

// all bits (including reserved bits) of MSGCTRL must be initialized to zero

ECanaMboxes.MBOX0.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX1.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX2.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX3.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX4.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX5.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX6.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX7.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX8.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX9.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX10.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX11.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX12.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX13.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX14.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX15.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX16.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX17.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX18.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX19.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX20.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX21.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX22.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX23.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX24.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX25.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX26.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX27.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX28.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX29.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX30.MSGCTRL.all = 0x00000000;

ECanaMboxes.MBOX31.MSGCTRL.all = 0x00000000;

// TAn, RMPn, GIFn bits are all zero upon reset and are cleared again

// as a matter of precaution.

ECanaRegs.CANTA.all = 0xFFFFFFFF; /* Clear all TAn bits */

ECanaRegs.CANRMP.all = 0xFFFFFFFF; /* Clear all RMPn bits */

ECanaRegs.CANGIF0.all = 0xFFFFFFFF; /* Clear all interrupt flag bits */

ECanaRegs.CANGIF1.all = 0xFFFFFFFF;

/* Configure bit timing parameters for eCANA*/

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.CCR = 1 ; // Set CCR = 1

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

do

{

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

} while(ECanaShadow.CANES.bit.CCE != 1 ); // Wait for CCE bit to be set..

ECanaShadow.CANBTC.all = 0;

#if (CPU_FRQ_150MHZ) // CPU_FRQ_150MHz is defined in DSP2833x_Examples.h

/* The following block for all 150 MHz SYSCLKOUT (75 MHz CAN clock) – default. Bit rate = 1 Mbps

See Note at End of File */

ECanaShadow.CANBTC.bit.BRPREG = 4;

ECanaShadow.CANBTC.bit.TSEG2REG = 2;

ECanaShadow.CANBTC.bit.TSEG1REG = 10;

#endif

#if (CPU_FRQ_100MHZ) // CPU_FRQ_100MHz is defined in DSP2833x_Examples.h

/* The following block is only for 100 MHz SYSCLKOUT (50 MHz CAN clock). Bit rate = 1 Mbps

See Note at End of File */

ECanaShadow.CANBTC.bit.BRPREG = 4;

ECanaShadow.CANBTC.bit.TSEG2REG = 1;

ECanaShadow.CANBTC.bit.TSEG1REG = 6;

#endif

ECanaShadow.CANBTC.bit.SAM = 1;

ECanaRegs.CANBTC.all = ECanaShadow.CANBTC.all;

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.CCR = 0 ; // Set CCR = 0

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

do

{

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

} while(ECanaShadow.CANES.bit.CCE != 0 ); // Wait for CCE bit to be cleared..

/* Disable all Mailboxes */

ECanaRegs.CANME.all = 0; // Required before writing the MSGIDs

EDIS;

//——————————————————————————————–

// Mailboxs can be written to 16-bits or 32-bits at a time

// ECanaMboxes.MBOX30.MSGID.all = 0x90000030; //Sent out

ECanaMboxes.MBOX29.MSGID.all = 0x01fffff29;

// ECanaMboxes.MBOX31.MSGID.all = 0x90000031; //Receive

// Configure Mailboxes 30/29 as Tx—0, 31 as Rx—-1

// Since this write is to the entire register (instead of a bit

// field) a shadow register is not required.

ECanaRegs.CANMD.all = 0x00000000;

// Enable 30/31 Mailboxes */

// Since this write is to the entire register (instead of a bit

// field) a shadow register is not required.

// ECanaRegs.CANME.all = 0xF0000000;

ECanaRegs.CANME.all = 0x20000000; //31 30 29 28 0010

// ECanaRegs.CANME.all = 0x40000000; //31 30 29 28 0100

// Specify that 8 bits will be sent/received

// ECanaMboxes.MBOX30.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX29.MSGCTRL.bit.DLC = 8;

// ECanaMboxes.MBOX30.MSGCTRL.bit.DLC = 8;

// ECanaMboxes.MBOX31.MSGCTRL.bit.DLC = 8;

}

yongyuan li:

回复 Johnson Chen1:

您好,AB板子是同一批板子,28335,硬件完全相同。单独都可以工作。速率为1MHz,120Ohm电阻都有,有尝试去掉也不行。程序换过来烧写还是同一块板子出错!

有没有可以是外设收发器SN65HVD230的问题呢??

谢谢!

TI中文支持网

TI中文支持网