各位

最近在做28346的一个项目,发现28346上电复位到执行gpio初始化代码期间,pwm的管脚默认输出为高,这就比较尴尬了,正常情况下,pwm控制igbt,如果硬件电路上没做下拉,那管子直接导通,母线和地短路了。ti设计时应该考虑到这一点的吧?怎么默认输出是高呢?我看过数据手册,gpio0-11默认上拉功能是disable的。有没有方法从软件方面修改这个输出电平呢?

而且还有一点,我发现从复位到执行到main函数,用的时间太长了,要200ms左右。

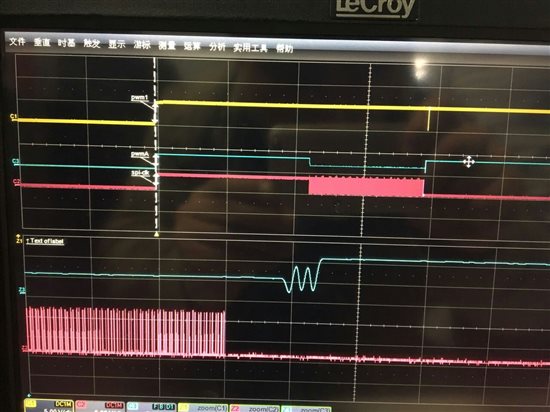

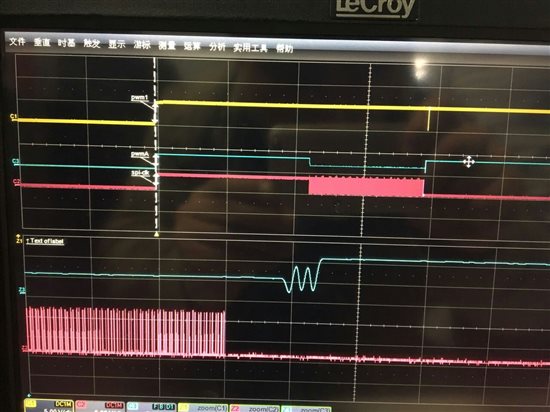

我做了一些测试,如下图

pwm1为dsp的gpio1管脚经过我板子上缓冲器的输出,

pwmA为直接测量的gpio1的输出

spiclk为346芯片上spi的时钟(我的28346,boot时通过spi来搬运外部程序)

从图中可以看到,上电复位后,gpio的输出就是高的,在程序从外部flash搬到ram期间(图中clk信号有效期间)为一个中间电平,然后程序执行(pwm1那个黄色的小刺是我初始化gpio的程序)

所有很困惑,芯片设计时为什么要默认复位时为高呢?除从硬件上,我在外围电路加一个下拉,还有没有可能从软件的角度去修改?

Hardy Zhou:

GPIO端口在reset状态下是默认为输入状态,有的GPIO在reset状态下带内部自动上拉,

所以GPIO1在reset状态下,是输入不带内部上拉,你可以断开GPIO1与缓冲器的连接,再测量看看是否上电时GPIO1出高电平或者电平不稳定.

各位

最近在做28346的一个项目,发现28346上电复位到执行gpio初始化代码期间,pwm的管脚默认输出为高,这就比较尴尬了,正常情况下,pwm控制igbt,如果硬件电路上没做下拉,那管子直接导通,母线和地短路了。ti设计时应该考虑到这一点的吧?怎么默认输出是高呢?我看过数据手册,gpio0-11默认上拉功能是disable的。有没有方法从软件方面修改这个输出电平呢?

而且还有一点,我发现从复位到执行到main函数,用的时间太长了,要200ms左右。

我做了一些测试,如下图

pwm1为dsp的gpio1管脚经过我板子上缓冲器的输出,

pwmA为直接测量的gpio1的输出

spiclk为346芯片上spi的时钟(我的28346,boot时通过spi来搬运外部程序)

从图中可以看到,上电复位后,gpio的输出就是高的,在程序从外部flash搬到ram期间(图中clk信号有效期间)为一个中间电平,然后程序执行(pwm1那个黄色的小刺是我初始化gpio的程序)

所有很困惑,芯片设计时为什么要默认复位时为高呢?除从硬件上,我在外围电路加一个下拉,还有没有可能从软件的角度去修改?

Eric Ma:

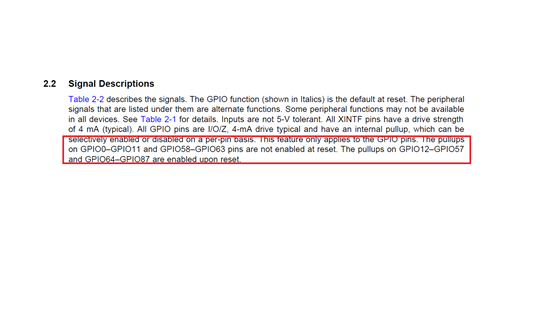

见手册:

Table 2-3 describes the signals. The GPIO function (shown in Italics) is the default at reset. The peripheralsignals that are listed under them are alternate functions. Some peripheral functions may not be availablein all devices. See Table 2-1 and Table 2-2 for details. Inputs are not 5-V tolerant. All pins capable ofproducing an XINTF output function have a drive strength of 8 mA (typical). This is true even if the pin isnot configured for XINTF functionality. All other pins have a drive strength of 4-mA drive typical (unlessotherwise indicated). All GPIO pins are I/O/Z and have an internal pullup, which can be selectivelyenabled or disabled on a per-pin basis. This feature only applies to the GPIO pins. The pullups onGPIO0–GPIO11 pins are not enabled at reset. The pullups on GPIO12–GPIO87 are enabled upon reset

芯片上电PWM引脚的上拉是没有启动的,你要看看你自己的初始化代码是否有吧

各位

最近在做28346的一个项目,发现28346上电复位到执行gpio初始化代码期间,pwm的管脚默认输出为高,这就比较尴尬了,正常情况下,pwm控制igbt,如果硬件电路上没做下拉,那管子直接导通,母线和地短路了。ti设计时应该考虑到这一点的吧?怎么默认输出是高呢?我看过数据手册,gpio0-11默认上拉功能是disable的。有没有方法从软件方面修改这个输出电平呢?

而且还有一点,我发现从复位到执行到main函数,用的时间太长了,要200ms左右。

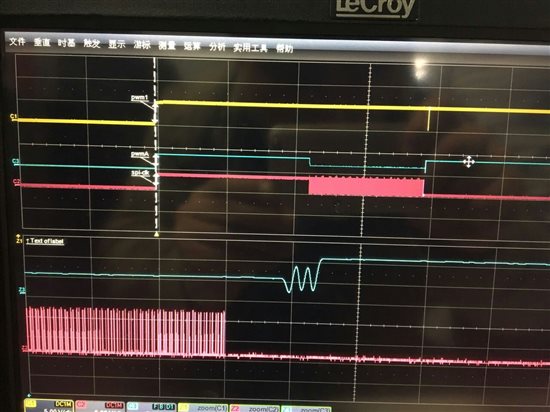

我做了一些测试,如下图

pwm1为dsp的gpio1管脚经过我板子上缓冲器的输出,

pwmA为直接测量的gpio1的输出

spiclk为346芯片上spi的时钟(我的28346,boot时通过spi来搬运外部程序)

从图中可以看到,上电复位后,gpio的输出就是高的,在程序从外部flash搬到ram期间(图中clk信号有效期间)为一个中间电平,然后程序执行(pwm1那个黄色的小刺是我初始化gpio的程序)

所有很困惑,芯片设计时为什么要默认复位时为高呢?除从硬件上,我在外围电路加一个下拉,还有没有可能从软件的角度去修改?

HEHE:

回复 Eric Ma:

但是,复位期间,我自己的初始化代码还没运行呢。我的意思是从上电到运行我自己程序这段时间里,pwm输出的是高。

各位

最近在做28346的一个项目,发现28346上电复位到执行gpio初始化代码期间,pwm的管脚默认输出为高,这就比较尴尬了,正常情况下,pwm控制igbt,如果硬件电路上没做下拉,那管子直接导通,母线和地短路了。ti设计时应该考虑到这一点的吧?怎么默认输出是高呢?我看过数据手册,gpio0-11默认上拉功能是disable的。有没有方法从软件方面修改这个输出电平呢?

而且还有一点,我发现从复位到执行到main函数,用的时间太长了,要200ms左右。

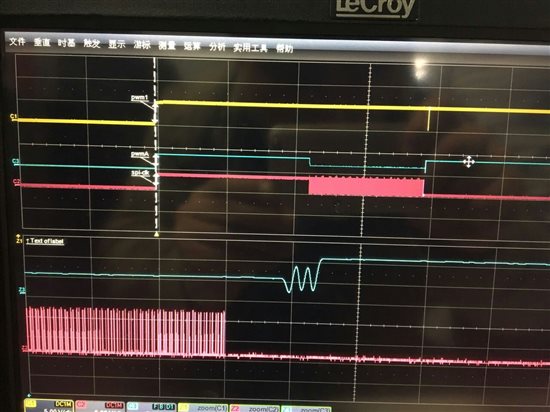

我做了一些测试,如下图

pwm1为dsp的gpio1管脚经过我板子上缓冲器的输出,

pwmA为直接测量的gpio1的输出

spiclk为346芯片上spi的时钟(我的28346,boot时通过spi来搬运外部程序)

从图中可以看到,上电复位后,gpio的输出就是高的,在程序从外部flash搬到ram期间(图中clk信号有效期间)为一个中间电平,然后程序执行(pwm1那个黄色的小刺是我初始化gpio的程序)

所有很困惑,芯片设计时为什么要默认复位时为高呢?除从硬件上,我在外围电路加一个下拉,还有没有可能从软件的角度去修改?

Eric Ma:

回复 HEHE:

那你看一下GPIO引脚的电平具体是多少,在初始化之前,不应该是3.3V的。

ERIC

TI中文支持网

TI中文支持网