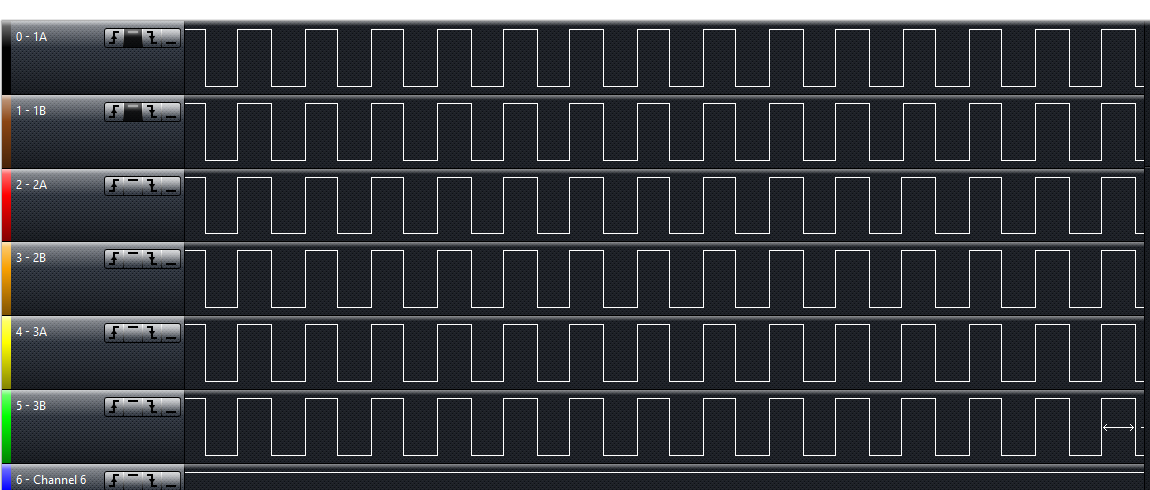

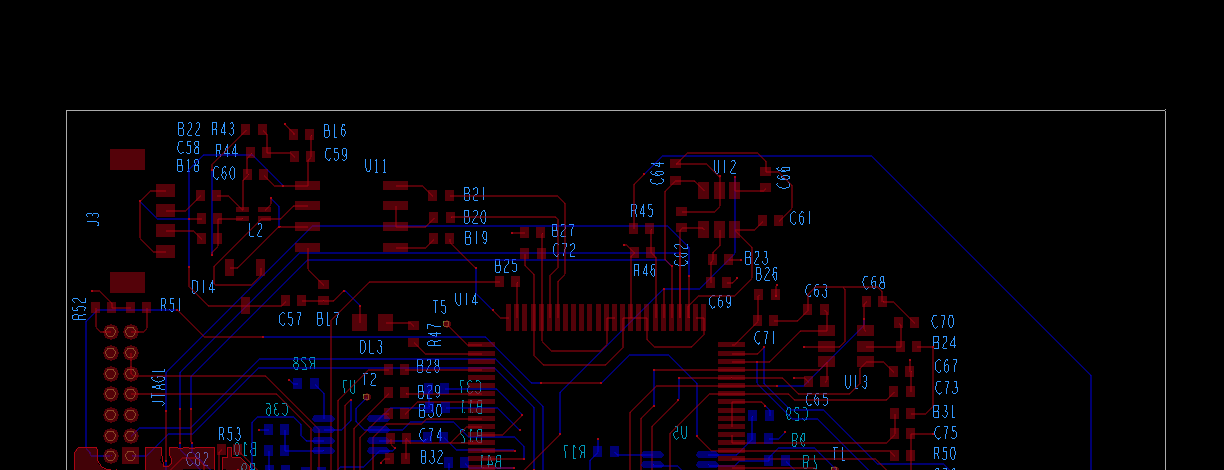

我是做28027F无感控制PMSM,用的是motor ware里面的lab1b程序,想给里面添加一个dlog,但是添加完以后,编译出现如下警告

Description Resource Path Location Type

#10247-D creating output section "DLOG" without a SECTIONS proj_lab01b C/C++ Problem

然后我在28027.cmd文件里面为dlog创建了一个sections,此时警告消失,编译没有问题,但是下载到板子上以后,程序就直接到一个中断里面死循环,

interrupt void PIE_illegalIsr(void)

{

{

// The next two lines are placeholders

asm(" ESTOP0");

asm(" ESTOP0");

// endless hold loop

for(;;);

for(;;);

} // end of PIE_illegalIsr() function

是我sections创建不对吗,应该改成什么样,我对照datasheet上面的。实在找不到地方了,请大神帮帮忙解解惑,万分感谢。

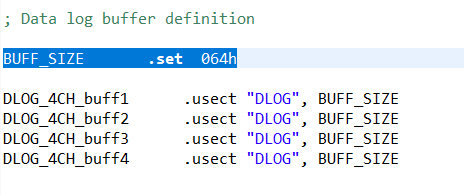

下面是我的.cmd文件,我试着给dlog添加过好多次sections,但都会死在中断里面,dlog的长度是400。

MEMORY

{

PAGE 0: /* Program Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE1 for data allocation */

{

PAGE 0: /* Program Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE1 for data allocation */

OTP : origin = 0x3D7800, length = 0x000400 /* on-chip OTP */

CSM_RSVD : origin = 0x3F7F80, length = 0x000076 /* Part of FLASHA. Program with all 0x0000 when CSM is in use. */

BEGIN : origin = 0x3F7FF6, length = 0x000002 /* Part of FLASHA. Used for "boot to Flash" bootloader mode. */

CSM_PWL_P0 : origin = 0x3F7FF8, length = 0x000008 /* Part of FLASHA. CSM password locations in FLASHA */

CSM_RSVD : origin = 0x3F7F80, length = 0x000076 /* Part of FLASHA. Program with all 0x0000 when CSM is in use. */

BEGIN : origin = 0x3F7FF6, length = 0x000002 /* Part of FLASHA. Used for "boot to Flash" bootloader mode. */

CSM_PWL_P0 : origin = 0x3F7FF8, length = 0x000008 /* Part of FLASHA. CSM password locations in FLASHA */

// L0 SARAM : origin = 0x3F8000, length = 0x000400

IQTABLES : origin = 0x3FE000, length = 0x000B50 /* IQ Math Tables in Boot ROM */

IQTABLES2 : origin = 0x3FEB50, length = 0x00008C /* IQ Math Tables in Boot ROM */

IQTABLES3 : origin = 0x3FEBDC, length = 0x0000AA /* IQ Math Tables in Boot ROM */

IQTABLES2 : origin = 0x3FEB50, length = 0x00008C /* IQ Math Tables in Boot ROM */

IQTABLES3 : origin = 0x3FEBDC, length = 0x0000AA /* IQ Math Tables in Boot ROM */

ROM : origin = 0x3FF27C, length = 0x000D44 /* Boot ROM */

RESET : origin = 0x3FFFC0, length = 0x000002 /* part of boot ROM */

VECTORS : origin = 0x3FFFC2, length = 0x00003E /* part of boot ROM */

// FLASHB_D : origin = 0x3F0000, length = 0x005C00

RESET : origin = 0x3FFFC0, length = 0x000002 /* part of boot ROM */

VECTORS : origin = 0x3FFFC2, length = 0x00003E /* part of boot ROM */

// FLASHB_D : origin = 0x3F0000, length = 0x005C00

FLASHB_D : origin = 0x3F0000, length = 0x006000 /* on-chip FLASH B, C and D */

D_FLASHA : origin = 0x3F6000, length = 0x001F80 /* on-chip FLASH A */

P_RAML0 : origin = 0x008000, length = 0x000980 /* on-chip PRAM block L0 */

D_FLASHA : origin = 0x3F6000, length = 0x001F80 /* on-chip FLASH A */

P_RAML0 : origin = 0x008000, length = 0x000980 /* on-chip PRAM block L0 */

//FLASHB_C : origin = 0x3F5C00, length = 0x000400

//G_RAML0 : origin = 0x3F8000, length = 0x000400

//G_RAML0 : origin = 0x3F8000, length = 0x000400

PAGE 1 : /* Data Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE0 for program allocation */

/* Registers remain on PAGE1 */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE0 for program allocation */

/* Registers remain on PAGE1 */

RAMM0_M1 : origin = 0x000000, length = 0x000600 /* on-chip RAM block M0 + M1. 0x600 to 0x800 reserved for InstaSPIN */

/* on-chip DRAM block L0 */

D_RAML0 : origin = 0x008980, length = 0x00680 /* on-chip RAM block M1 */

// G_RAML0 : origin = 0x3F8C00, length = 0x000400

}

}

/* Allocate sections to memory blocks.

Note:

codestart user defined section in DSP28_CodeStartBranch.asm used to redirect code

execution when booting to flash

ramfuncs user defined section to store functions that will be copied from Flash into RAM

*/

Note:

codestart user defined section in DSP28_CodeStartBranch.asm used to redirect code

execution when booting to flash

ramfuncs user defined section to store functions that will be copied from Flash into RAM

*/

SECTIONS

{

/* Allocate program areas: */

.cinit : > FLASHB_D PAGE = 0

.pinit : > FLASHB_D, PAGE = 0

.text : > FLASHB_D PAGE = 0

codestart : > BEGIN PAGE = 0

ramfuncs : LOAD = FLASHB_D,

RUN = P_RAML0,

LOAD_START(_RamfuncsLoadStart),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

PAGE = 0

{

/* Allocate program areas: */

.cinit : > FLASHB_D PAGE = 0

.pinit : > FLASHB_D, PAGE = 0

.text : > FLASHB_D PAGE = 0

codestart : > BEGIN PAGE = 0

ramfuncs : LOAD = FLASHB_D,

RUN = P_RAML0,

LOAD_START(_RamfuncsLoadStart),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

PAGE = 0

csmpasswds : > CSM_PWL_P0 PAGE = 0

csm_rsvd : > CSM_RSVD PAGE = 0

csm_rsvd : > CSM_RSVD PAGE = 0

/* Allocate uninitalized data sections: */

.stack : > D_RAML0 PAGE = 1

.ebss : > RAMM0_M1 PAGE = 1

// .ebss : > RAMM0 PAGE = 1

.esysmem : > RAMM0_M1 PAGE = 1

// .esysmem : > RAMM0 PAGE = 1

.stack : > D_RAML0 PAGE = 1

.ebss : > RAMM0_M1 PAGE = 1

// .ebss : > RAMM0 PAGE = 1

.esysmem : > RAMM0_M1 PAGE = 1

// .esysmem : > RAMM0 PAGE = 1

ebss_extension : > P_RAML0 PAGE = 0

rom_accessed_data : > RAMM0_M1 PAGE = 1

// rom_accessed_data : > RAMM0 PAGE = 1

vib_buf_data : > D_RAML0 PAGE = 1

graph_data : > D_RAML0 PAGE = 1

rom_accessed_data : > RAMM0_M1 PAGE = 1

// rom_accessed_data : > RAMM0 PAGE = 1

vib_buf_data : > D_RAML0 PAGE = 1

graph_data : > D_RAML0 PAGE = 1

/* Initalized sections go in Flash */

/* For SDFlash to program these, they must be allocated to page 0 */

.econst : > D_FLASHA, PAGE = 0

.switch : > D_FLASHA, PAGE = 0

/* For SDFlash to program these, they must be allocated to page 0 */

.econst : > D_FLASHA, PAGE = 0

.switch : > D_FLASHA, PAGE = 0

/* Allocate IQ math areas: */

IQmath : > FLASHB_D PAGE = 0 /* Math Code */

IQmathTables : > IQTABLES, PAGE = 0, TYPE = NOLOAD

IQmath : > FLASHB_D PAGE = 0 /* Math Code */

IQmathTables : > IQTABLES, PAGE = 0, TYPE = NOLOAD

/* Uncomment the section below if calling the IQNexp() or IQexp()

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables2

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables2 : > IQTABLES2, PAGE = 0, TYPE = NOLOAD

{

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables2

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables2 : > IQTABLES2, PAGE = 0, TYPE = NOLOAD

{

IQmath.lib<IQNexpTable.obj> (IQmathTablesRam)

}

*/

/* Uncomment the section below if calling the IQNasin() or IQasin()

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables3

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables3 : > IQTABLES3, PAGE = 0, TYPE = NOLOAD

{

*/

/* Uncomment the section below if calling the IQNasin() or IQasin()

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables3

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables3 : > IQTABLES3, PAGE = 0, TYPE = NOLOAD

{

IQmath.lib<IQNasinTable.obj> (IQmathTablesRam)

}

*/

*/

/* .reset is a standard section used by the compiler. It contains the */

/* the address of the start of _c_int00 for C Code. */

/* When using the boot ROM this section and the CPU vector */

/* table is not needed. Thus the default type is set here to */

/* DSECT */

.reset : > RESET, PAGE = 0, TYPE = DSECT

vectors : > VECTORS PAGE = 0, TYPE = DSECT

/* the address of the start of _c_int00 for C Code. */

/* When using the boot ROM this section and the CPU vector */

/* table is not needed. Thus the default type is set here to */

/* DSECT */

.reset : > RESET, PAGE = 0, TYPE = DSECT

vectors : > VECTORS PAGE = 0, TYPE = DSECT

}

SECTIONS

{

DLOG: > D_RAML0,PAGE=1

}

{

DLOG: > D_RAML0,PAGE=1

}

Young Hu:

1. F28027F的RAM很小,建议把DLOG的长度小一些;

2. 把stack设置小一些;

3. 看一下是从哪儿进入faultISR的?

我是做28027F无感控制PMSM,用的是motor ware里面的lab1b程序,想给里面添加一个dlog,但是添加完以后,编译出现如下警告

Description Resource Path Location Type

#10247-D creating output section "DLOG" without a SECTIONS proj_lab01b C/C++ Problem

然后我在28027.cmd文件里面为dlog创建了一个sections,此时警告消失,编译没有问题,但是下载到板子上以后,程序就直接到一个中断里面死循环,

interrupt void PIE_illegalIsr(void)

{

{

// The next two lines are placeholders

asm(" ESTOP0");

asm(" ESTOP0");

// endless hold loop

for(;;);

for(;;);

} // end of PIE_illegalIsr() function

是我sections创建不对吗,应该改成什么样,我对照datasheet上面的。实在找不到地方了,请大神帮帮忙解解惑,万分感谢。

下面是我的.cmd文件,我试着给dlog添加过好多次sections,但都会死在中断里面,dlog的长度是400。

MEMORY

{

PAGE 0: /* Program Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE1 for data allocation */

{

PAGE 0: /* Program Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE1 for data allocation */

OTP : origin = 0x3D7800, length = 0x000400 /* on-chip OTP */

CSM_RSVD : origin = 0x3F7F80, length = 0x000076 /* Part of FLASHA. Program with all 0x0000 when CSM is in use. */

BEGIN : origin = 0x3F7FF6, length = 0x000002 /* Part of FLASHA. Used for "boot to Flash" bootloader mode. */

CSM_PWL_P0 : origin = 0x3F7FF8, length = 0x000008 /* Part of FLASHA. CSM password locations in FLASHA */

CSM_RSVD : origin = 0x3F7F80, length = 0x000076 /* Part of FLASHA. Program with all 0x0000 when CSM is in use. */

BEGIN : origin = 0x3F7FF6, length = 0x000002 /* Part of FLASHA. Used for "boot to Flash" bootloader mode. */

CSM_PWL_P0 : origin = 0x3F7FF8, length = 0x000008 /* Part of FLASHA. CSM password locations in FLASHA */

// L0 SARAM : origin = 0x3F8000, length = 0x000400

IQTABLES : origin = 0x3FE000, length = 0x000B50 /* IQ Math Tables in Boot ROM */

IQTABLES2 : origin = 0x3FEB50, length = 0x00008C /* IQ Math Tables in Boot ROM */

IQTABLES3 : origin = 0x3FEBDC, length = 0x0000AA /* IQ Math Tables in Boot ROM */

IQTABLES2 : origin = 0x3FEB50, length = 0x00008C /* IQ Math Tables in Boot ROM */

IQTABLES3 : origin = 0x3FEBDC, length = 0x0000AA /* IQ Math Tables in Boot ROM */

ROM : origin = 0x3FF27C, length = 0x000D44 /* Boot ROM */

RESET : origin = 0x3FFFC0, length = 0x000002 /* part of boot ROM */

VECTORS : origin = 0x3FFFC2, length = 0x00003E /* part of boot ROM */

// FLASHB_D : origin = 0x3F0000, length = 0x005C00

RESET : origin = 0x3FFFC0, length = 0x000002 /* part of boot ROM */

VECTORS : origin = 0x3FFFC2, length = 0x00003E /* part of boot ROM */

// FLASHB_D : origin = 0x3F0000, length = 0x005C00

FLASHB_D : origin = 0x3F0000, length = 0x006000 /* on-chip FLASH B, C and D */

D_FLASHA : origin = 0x3F6000, length = 0x001F80 /* on-chip FLASH A */

P_RAML0 : origin = 0x008000, length = 0x000980 /* on-chip PRAM block L0 */

D_FLASHA : origin = 0x3F6000, length = 0x001F80 /* on-chip FLASH A */

P_RAML0 : origin = 0x008000, length = 0x000980 /* on-chip PRAM block L0 */

//FLASHB_C : origin = 0x3F5C00, length = 0x000400

//G_RAML0 : origin = 0x3F8000, length = 0x000400

//G_RAML0 : origin = 0x3F8000, length = 0x000400

PAGE 1 : /* Data Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE0 for program allocation */

/* Registers remain on PAGE1 */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE0 for program allocation */

/* Registers remain on PAGE1 */

RAMM0_M1 : origin = 0x000000, length = 0x000600 /* on-chip RAM block M0 + M1. 0x600 to 0x800 reserved for InstaSPIN */

/* on-chip DRAM block L0 */

D_RAML0 : origin = 0x008980, length = 0x00680 /* on-chip RAM block M1 */

// G_RAML0 : origin = 0x3F8C00, length = 0x000400

}

}

/* Allocate sections to memory blocks.

Note:

codestart user defined section in DSP28_CodeStartBranch.asm used to redirect code

execution when booting to flash

ramfuncs user defined section to store functions that will be copied from Flash into RAM

*/

Note:

codestart user defined section in DSP28_CodeStartBranch.asm used to redirect code

execution when booting to flash

ramfuncs user defined section to store functions that will be copied from Flash into RAM

*/

SECTIONS

{

/* Allocate program areas: */

.cinit : > FLASHB_D PAGE = 0

.pinit : > FLASHB_D, PAGE = 0

.text : > FLASHB_D PAGE = 0

codestart : > BEGIN PAGE = 0

ramfuncs : LOAD = FLASHB_D,

RUN = P_RAML0,

LOAD_START(_RamfuncsLoadStart),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

PAGE = 0

{

/* Allocate program areas: */

.cinit : > FLASHB_D PAGE = 0

.pinit : > FLASHB_D, PAGE = 0

.text : > FLASHB_D PAGE = 0

codestart : > BEGIN PAGE = 0

ramfuncs : LOAD = FLASHB_D,

RUN = P_RAML0,

LOAD_START(_RamfuncsLoadStart),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

PAGE = 0

csmpasswds : > CSM_PWL_P0 PAGE = 0

csm_rsvd : > CSM_RSVD PAGE = 0

csm_rsvd : > CSM_RSVD PAGE = 0

/* Allocate uninitalized data sections: */

.stack : > D_RAML0 PAGE = 1

.ebss : > RAMM0_M1 PAGE = 1

// .ebss : > RAMM0 PAGE = 1

.esysmem : > RAMM0_M1 PAGE = 1

// .esysmem : > RAMM0 PAGE = 1

.stack : > D_RAML0 PAGE = 1

.ebss : > RAMM0_M1 PAGE = 1

// .ebss : > RAMM0 PAGE = 1

.esysmem : > RAMM0_M1 PAGE = 1

// .esysmem : > RAMM0 PAGE = 1

ebss_extension : > P_RAML0 PAGE = 0

rom_accessed_data : > RAMM0_M1 PAGE = 1

// rom_accessed_data : > RAMM0 PAGE = 1

vib_buf_data : > D_RAML0 PAGE = 1

graph_data : > D_RAML0 PAGE = 1

rom_accessed_data : > RAMM0_M1 PAGE = 1

// rom_accessed_data : > RAMM0 PAGE = 1

vib_buf_data : > D_RAML0 PAGE = 1

graph_data : > D_RAML0 PAGE = 1

/* Initalized sections go in Flash */

/* For SDFlash to program these, they must be allocated to page 0 */

.econst : > D_FLASHA, PAGE = 0

.switch : > D_FLASHA, PAGE = 0

/* For SDFlash to program these, they must be allocated to page 0 */

.econst : > D_FLASHA, PAGE = 0

.switch : > D_FLASHA, PAGE = 0

/* Allocate IQ math areas: */

IQmath : > FLASHB_D PAGE = 0 /* Math Code */

IQmathTables : > IQTABLES, PAGE = 0, TYPE = NOLOAD

IQmath : > FLASHB_D PAGE = 0 /* Math Code */

IQmathTables : > IQTABLES, PAGE = 0, TYPE = NOLOAD

/* Uncomment the section below if calling the IQNexp() or IQexp()

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables2

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables2 : > IQTABLES2, PAGE = 0, TYPE = NOLOAD

{

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables2

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables2 : > IQTABLES2, PAGE = 0, TYPE = NOLOAD

{

IQmath.lib<IQNexpTable.obj> (IQmathTablesRam)

}

*/

/* Uncomment the section below if calling the IQNasin() or IQasin()

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables3

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables3 : > IQTABLES3, PAGE = 0, TYPE = NOLOAD

{

*/

/* Uncomment the section below if calling the IQNasin() or IQasin()

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables3

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables3 : > IQTABLES3, PAGE = 0, TYPE = NOLOAD

{

IQmath.lib<IQNasinTable.obj> (IQmathTablesRam)

}

*/

*/

/* .reset is a standard section used by the compiler. It contains the */

/* the address of the start of _c_int00 for C Code. */

/* When using the boot ROM this section and the CPU vector */

/* table is not needed. Thus the default type is set here to */

/* DSECT */

.reset : > RESET, PAGE = 0, TYPE = DSECT

vectors : > VECTORS PAGE = 0, TYPE = DSECT

/* the address of the start of _c_int00 for C Code. */

/* When using the boot ROM this section and the CPU vector */

/* table is not needed. Thus the default type is set here to */

/* DSECT */

.reset : > RESET, PAGE = 0, TYPE = DSECT

vectors : > VECTORS PAGE = 0, TYPE = DSECT

}

SECTIONS

{

DLOG: > D_RAML0,PAGE=1

}

{

DLOG: > D_RAML0,PAGE=1

}

bob iuuiy:

回复 Young Hu:

1.delog大小是在.asm中改变吗?

2

stack的大小在哪里改呢?

TI中文支持网

TI中文支持网