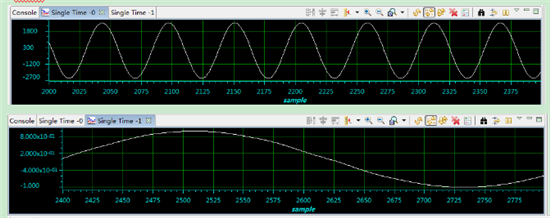

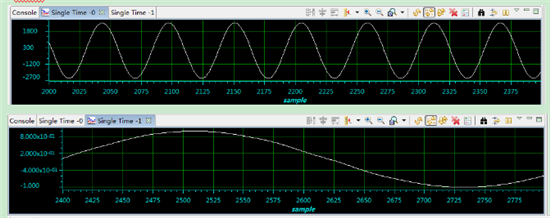

上图第一个是采集的频率50HZ的正弦交流电压波形,下图是对应的SPLL锁相环的SIN输出,即是下面结构体的sin元素。

typedef struct{

float32 u[3]; // Ac Input

float32 osg_u[3];

float32 osg_qu[3];

float32 u_Q[2];

float32 u_D[2];

float32 ylf[2];

float32 fo; // output frequency of PLL

float32 fn; //nominal frequency

float32 theta[2];

float32 cos;

float32 sin;

float32 delta_T;

SPLL_1ph_SOGI_F_OSG_COEFF osg_coeff;

SPLL_1ph_SOGI_F_LPF_COEFF lpf_coeff;

}SPLL_1ph_SOGI_F;

不知这个输出正确否,正弦波都输出好几个周期的波形了,SPLL才输出一个周期。谁能解释下,或者说下自己使用SPLL的经验,非常感谢

Terry Deng:

应该不对吧,SPLL输出与采集的信号频率也差太多了。

1,你确定是运行在闭环模式吗; 2,SPLL输入的是采集的信号吗;3,试试调整LPF的系数

上图第一个是采集的频率50HZ的正弦交流电压波形,下图是对应的SPLL锁相环的SIN输出,即是下面结构体的sin元素。

typedef struct{

float32 u[3]; // Ac Input

float32 osg_u[3];

float32 osg_qu[3];

float32 u_Q[2];

float32 u_D[2];

float32 ylf[2];

float32 fo; // output frequency of PLL

float32 fn; //nominal frequency

float32 theta[2];

float32 cos;

float32 sin;

float32 delta_T;

SPLL_1ph_SOGI_F_OSG_COEFF osg_coeff;

SPLL_1ph_SOGI_F_LPF_COEFF lpf_coeff;

}SPLL_1ph_SOGI_F;

不知这个输出正确否,正弦波都输出好几个周期的波形了,SPLL才输出一个周期。谁能解释下,或者说下自己使用SPLL的经验,非常感谢

feng shi:

回复 Terry Deng:

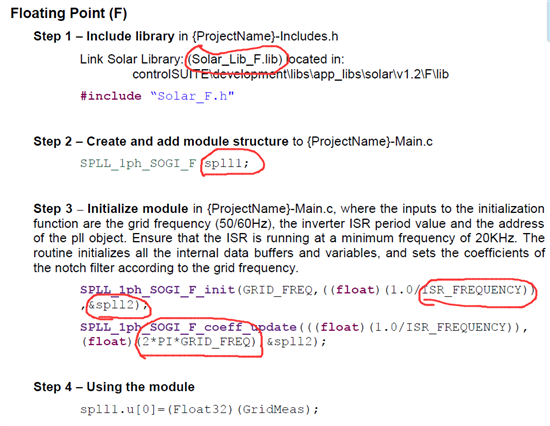

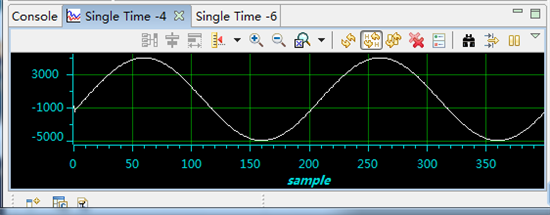

这是我的设置

SPLL_1ph_SOGI_F_init(GRID_FREQ, (float32)(1.0/ISR_FREQUENCY), &spll1); SPLL_1ph_SOGI_F_coeff_update((float32)(1.0/ISR_FREQUENCY), 2*50*3.1415926,&spll1);

GridMeas=((float32)s_volt[0])/5000.0f;//由mV转化为V,再限制在-1到1内 spll1.u[0]=GridMeas; SPLL_1ph_SOGI_F_FUNC(&spll1);

检测的就是s_volt[0],上面的输出就是这个正弦波形。ISR_FREQUENCY没达到设定的频率,会影响这个输出吗,

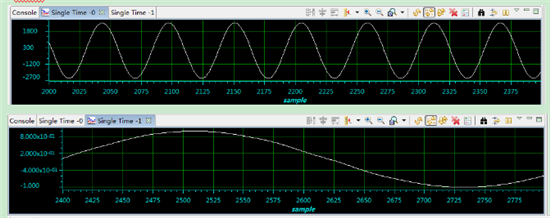

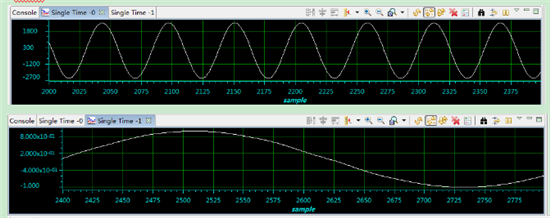

上图第一个是采集的频率50HZ的正弦交流电压波形,下图是对应的SPLL锁相环的SIN输出,即是下面结构体的sin元素。

typedef struct{

float32 u[3]; // Ac Input

float32 osg_u[3];

float32 osg_qu[3];

float32 u_Q[2];

float32 u_D[2];

float32 ylf[2];

float32 fo; // output frequency of PLL

float32 fn; //nominal frequency

float32 theta[2];

float32 cos;

float32 sin;

float32 delta_T;

SPLL_1ph_SOGI_F_OSG_COEFF osg_coeff;

SPLL_1ph_SOGI_F_LPF_COEFF lpf_coeff;

}SPLL_1ph_SOGI_F;

不知这个输出正确否,正弦波都输出好几个周期的波形了,SPLL才输出一个周期。谁能解释下,或者说下自己使用SPLL的经验,非常感谢

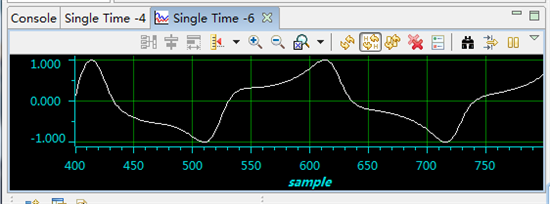

feng shi:

回复 feng shi:

把中断频率改小之后就成了这样的,

下面的是SPLL的正弦输出,上面是采样的值。这个该调节什么呢?中断频率没法达到要求的20KHZ

上图第一个是采集的频率50HZ的正弦交流电压波形,下图是对应的SPLL锁相环的SIN输出,即是下面结构体的sin元素。

typedef struct{

float32 u[3]; // Ac Input

float32 osg_u[3];

float32 osg_qu[3];

float32 u_Q[2];

float32 u_D[2];

float32 ylf[2];

float32 fo; // output frequency of PLL

float32 fn; //nominal frequency

float32 theta[2];

float32 cos;

float32 sin;

float32 delta_T;

SPLL_1ph_SOGI_F_OSG_COEFF osg_coeff;

SPLL_1ph_SOGI_F_LPF_COEFF lpf_coeff;

}SPLL_1ph_SOGI_F;

不知这个输出正确否,正弦波都输出好几个周期的波形了,SPLL才输出一个周期。谁能解释下,或者说下自己使用SPLL的经验,非常感谢

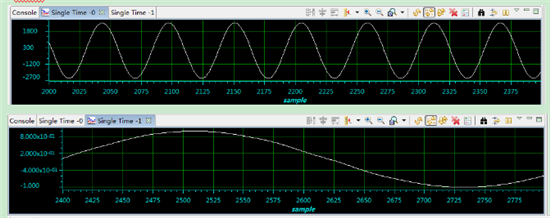

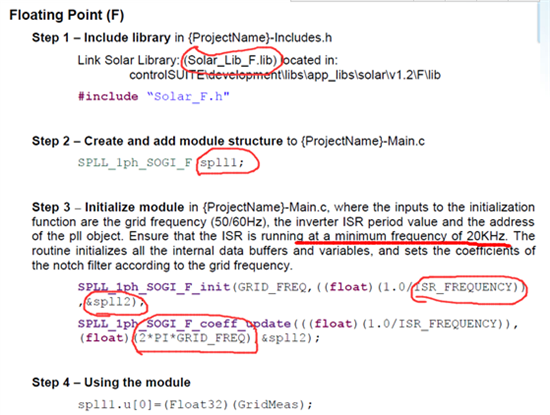

feng shi:

回复 feng shi:

这个有人知道吗?达到要求的中断频率时是正确的。但是达不到要求的频率时怎么修改,谢谢

上图第一个是采集的频率50HZ的正弦交流电压波形,下图是对应的SPLL锁相环的SIN输出,即是下面结构体的sin元素。

typedef struct{

float32 u[3]; // Ac Input

float32 osg_u[3];

float32 osg_qu[3];

float32 u_Q[2];

float32 u_D[2];

float32 ylf[2];

float32 fo; // output frequency of PLL

float32 fn; //nominal frequency

float32 theta[2];

float32 cos;

float32 sin;

float32 delta_T;

SPLL_1ph_SOGI_F_OSG_COEFF osg_coeff;

SPLL_1ph_SOGI_F_LPF_COEFF lpf_coeff;

}SPLL_1ph_SOGI_F;

不知这个输出正确否,正弦波都输出好几个周期的波形了,SPLL才输出一个周期。谁能解释下,或者说下自己使用SPLL的经验,非常感谢

user3784592:

回复 feng shi:

楼主,当中断频率达不到20kHz,spll是怎么处理的?

TI中文支持网

TI中文支持网