Hi

使用C2000遇到的SCI的FIFO问题,请帮忙解答

基础配置:2.5M波特率,8位数据,无奇偶校验,1位停止位

开启SCI的FIFO增加模式,SciaRegs.SCIFFTX.all = 0xE040;发送中断等级TXFFIL配置为0;

当发送4帧数据到SciaRegs.SCITXBUF时,通时开启SciaRegs.SCIFFTX.bit.TXFFIENA中断使能,发现数据还未发送完就会提前进中断,必须在中断里面增加while(!SciaRegs.SCICTL2.bit.TXEMPTY);语句判断才能把数据发送完毕。

因为这边采用半双工模式发送数据,若数据不发送完毕直接切换芯片收发脚就会导致最后一桢数据会丢失部分,目前在中断里面增加while(!SciaRegs.SCICTL2.bit.TXEMPTY)语句判断,这样就会在中断里面等待较长的时间,造成资源浪费。有没有其他方法或者例程参考可以解决上述问题?

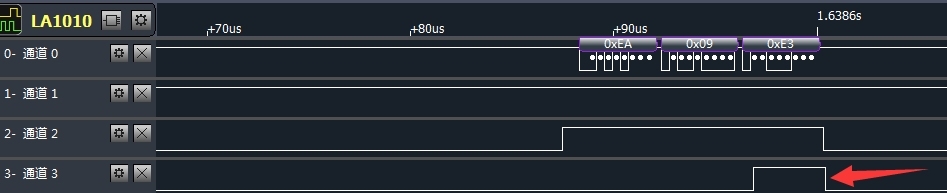

上图通道1使用FIFO发送的4帧数据,通道2是485芯片片选脚,通道3是为了测试在中断里面等待的时间,送色箭头指示的是在中断里等待的时间。必须等待一桢发送完毕,不然最后一桢会丢失。

外设配置如下

void InitSetScia(void)

{

// 应该放在前面

SciStatus = SCI_READ_DATA_INIT;

EALLOW;

SciaRegs.SCICTL1.bit.SWRESET =0; //复位SCI

SciaRegs.SCICTL1.bit.RXENA=0; //SCI接收器使能

SciaRegs.SCICTL1.bit.TXENA=0; //SCI发送器使能

//设置FIFO寄存器

SciaRegs.SCIFFTX.all = 0xE040;

//SciaRegs.SCIFFTX.all = 0x0000;

//SciaRegs.SCIFFTX.bit.TXFFINTCLR = 1;//清除发送中断标志

//SciaRegs.SCIFFTX.bit.TXFIFOReset = 1;//重新使能FIFO发送操作

//SciaRegs.SCIFFTX.bit.SCIFFENA = 1; //增强FIFO使能

//SciaRegs.SCIFFTX.bit.SCIRST = 1; //恢复FIFO接收和发送

SciaRegs.SCIFFTX.bit.TXFFIL=0;

//SciaRegs.SCIFFTX.bit.TXFFIENA=1; //发送缓冲中断开启

SciaRegs.SCIFFRX.all = 0x405F; // Receive FIFO reset

//SciaRegs.SPIFFRX.bit.RXFFIL40 = 0b11111 //

//SciaRegs.SPIFFRX.bit.RXFFINTCLR = 1;//清除接收中断标志

//SciaRegs.SPIFFRX.bit.RXFFOVF CLR = 1;//接收溢出标志位清除

SciaRegs.SCIFFRX.all = 0x205F; // Re-enable transmit FIFO operation

//SciaRegs.SPIFFRX.bit.RXFIFOReset = 1;//重新使能FIFO接收操作

SciaRegs.SCIFFCT.all = 0x0000; //字符之间零延迟传输 应当适当添加延时周期

//SciaRegs.SCICTL2.bit.TXINTENA =1; //Enable TXTDY中断

//SciaRegs.SCICTL2.bit.RXBKINTENA =1; //Enable RXTDY中断

SciaRegs.SCICTL2.bit.TXEMPTY = 1; //发送缓冲和移位寄存器都为空时 置空闲标志位

SciaRegs.SCICTL2.bit.TXRDY = 1; //置标志位准备好接收下一个需发送数据

SciaRegs.SCICCR.all = 0x0007; // 1 stop bit, No loopback, No parity,8 bits,async mode,idle-line

//BIT5:有无校验位 BIT6:0奇校验 1偶校验 BIT7:0:1位停止位 1:2位停止位

SciaRegs.SCIHBAUD = 0;//dspBaudRegData[tmp].high;

SciaRegs.SCILBAUD = 2;//dspBaudRegData[tmp].low; 2.5M

SciaRegs.SCIPRI.bit.FREE = 1;

//SciaRegs.SCICTL1.all =0x0021; // Relinquish SCI from Reset

SciaRegs.SCICTL1.bit.RXENA = 1; //SCI接收器使能

SciaRegs.SCICTL1.bit.TXENA = 1; //SCI发送器使能

SciaRegs.SCICTL1.bit.SLEEP = 0; //休眠模式关闭

SciaRegs.SCICTL1.bit.SWRESET =1; //复位SCI

EDIS;

}

interrupt void SCI_TXD_isr(void)

{

EINT;

GpioDataRegs.GPADAT.bit.GPIO26 = 1; // 测试

SciaRegs.SCIFFTX.bit.TXFFIENA=0;//发送中断关闭

while(!SciaRegs.SCICTL2.bit.TXEMPTY);

SciaRegs.SCIFFTX.bit.TXFFINTCLR = 1;//清除发送中断标志

RTS = RS485_R;

SciStatus=SCI_SEND_OK;//数据发送完毕

GpioDataRegs.GPADAT.bit.GPIO26 = 0; // 测试

PieCtrlRegs.PIEACK.bit.ACK9 = 1; // Issue PIE ACK

}

Annie Liu:

为更加有效地解决您的问题,我们建议您将问题发布在E2E英文技术论坛上https://e2e.ti.com/support/microcontrollers/c2000/f/171,将由资深的工程师为您提供帮助。我们的E2E英文社区有TI专家进行回复,并得到全球各地工程师的支持,分享他们的知识和经验。

TI中文支持网

TI中文支持网