我是做硬件的。这是第一次设计2812板子,软件开发人员说板子的EVB能正常输出,EVA无输出。经过我检查硬件发现如果将110脚(GPIOD0-T1CTRIP-PDPINTA)为低电平时EVA无输出。110脚拉高的话EVA也就正常了。我的疑问是出现这种情况的原因是我硬件设计不合理,还是软件上配置不合理?

先说说我的硬件:硬件上我将110设计成了通用IO的输入引脚。 如果我想用EVA的话,110脚可不可以设计成为GPIO的输入引脚,?

硬件不改动的话,软件上应该如何设置,才能不影响EVA?

Jones Chen:

您好,您的110脚配置成什么接口?Gpio还是PDPINT? 如果是GPIO应该么有问题。

这个是因为PDPINT引脚为外部异常保护引脚,如果配置成PDPINT,有异常信号,会切断PWM的输出。

因此,如果硬件不能改动,在软件上,配置成GPIO就应该可以。

我是做硬件的。这是第一次设计2812板子,软件开发人员说板子的EVB能正常输出,EVA无输出。经过我检查硬件发现如果将110脚(GPIOD0-T1CTRIP-PDPINTA)为低电平时EVA无输出。110脚拉高的话EVA也就正常了。我的疑问是出现这种情况的原因是我硬件设计不合理,还是软件上配置不合理?

先说说我的硬件:硬件上我将110设计成了通用IO的输入引脚。 如果我想用EVA的话,110脚可不可以设计成为GPIO的输入引脚,?

硬件不改动的话,软件上应该如何设置,才能不影响EVA?

gong cao:

回复 Jones Chen:

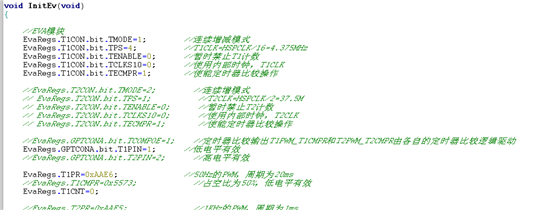

110脚配置成Gpio了,按理说应该不会影响PWM的输出。但是,现在的情况是影响了,我不清楚为什么。

我是做硬件的。这是第一次设计2812板子,软件开发人员说板子的EVB能正常输出,EVA无输出。经过我检查硬件发现如果将110脚(GPIOD0-T1CTRIP-PDPINTA)为低电平时EVA无输出。110脚拉高的话EVA也就正常了。我的疑问是出现这种情况的原因是我硬件设计不合理,还是软件上配置不合理?

先说说我的硬件:硬件上我将110设计成了通用IO的输入引脚。 如果我想用EVA的话,110脚可不可以设计成为GPIO的输入引脚,?

硬件不改动的话,软件上应该如何设置,才能不影响EVA?

Jones Chen:

回复 gong cao:

正常情况下是不会影响的,请在运行的时候,查询一下GPIOMUX寄存器是否已经成功设置。

TI中文支持网

TI中文支持网