各位TI的大牛们,请解答一下下面的问题!

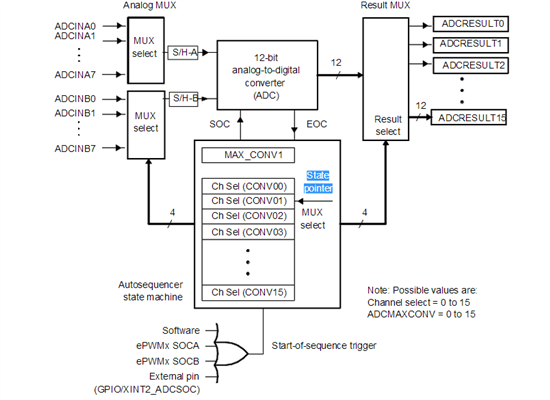

在我的设计中,ADC1采用overlap、依次顺序进行转换,各SOC0–SOC15均采用定时器TINT1的100us定时去触发,当SOC15转换完毕后去触发ADCINT1,ADCINT1在PIE中不允许中断,通过查询标记位判断16个SOC转换是否完成。在程序中在各步加设GIO置1或0的方式,通过示波器观察各步的执行时间和状态,发现采用查询ADCINT1中断标记位时,从ADC启动(通过TINT1启动)到ADC1 的中断标记置位时的时间间隔只有惊人的0.8us这么短,那可是16个SOC的转换啊!根据TI的SPRUH22F中P900到的参数,应该是543ns X 16=8.5us左右,差距是10倍左右!而采用查询ADCCTL1.bit.ADCBSY和ADCCTL1.bit.ADCBSYCHN方式,时间大约8us,较合理! ADCINT1和TINT1均允许中断,但在PIE中却不允许中断,通过查询方式,因中断和主程序在来回跳转时,也将消耗时间。

我的问题就是:如何通过查询相关的ADCINT1中断标记位,判断16个SOC转换是否完成?

以下是相关的程序代码,欢迎各位大牛们指教!谢谢! 硬件用的是Concerto F28M35xx controlCARD。软件是在\ti\controlSUITE\device_support\f28m36x\v206修改的。

EALLOW;

Adc1Regs.ADCCTL1.bit.ADCBGPWD = 1; // Power ADC1 BG, Bandgap circuit(带隙基准电路) 上电, 见TRM P911 ADCCTL1

Adc1Regs.ADCCTL1.bit.ADCREFPWD = 1; // Power reference,Reference buffers circuit power down

Adc1Regs.ADCCTL1.bit.ADCPWDN = 1; // Power ADC1, ADC power down

Adc1Regs.ADCCTL1.bit.ADCENABLE = 1; // Enable ADC1

Adc1Regs.ADCCTL1.bit.ADCREFSEL = 0; // Select interal BG, Internal/external reference select

Adc1Regs.ADCCTL2.bit.ADCNONOVERLAP = 0; // 0–Enable overlap mode

Adc1Regs.ADCCTL1.bit.INTPULSEPOS = 1; // ADCINT1 trips after AdcResults latch

Adc1Regs.INTSEL1N2.bit.INT1E = 1; // Enabled ADCINT1

Adc1Regs.INTSEL1N2.bit.INT1CONT = 0; // Disable ADCINT1 Continuous mode

Adc1Regs.INTSEL1N2.bit.INT1SEL = 15; // setup ADC1 EOC15 to trigger ADCINT1

Adc1Regs.SOCPRICTL.bit.SOCPRIORITY = 15; // 15: SOC0-SOC14 are high priority, SOC15 is in round robin mode.

AnalogSysctrlRegs.TRIG1SEL.all = 2; // Assigning TINT1 (CPU Timer 1) to ADC TRIGGER 1 of the ADC1 and ADC2 module

Adc1Regs.ADCSOC0CTL.bit.CHSEL = 0; // set SOC0 channel select to ADC1A0

Adc1Regs.ADCSOC1CTL.bit.CHSEL = 8; // set SOC1 channel select to ADC1B0

Adc1Regs.ADCSOC2CTL.bit.CHSEL = 4; // set SOC2 channel select to ADC1A4

Adc1Regs.ADCSOC3CTL.bit.CHSEL = 12; // set SOC3 channel select to ADC1B4

Adc1Regs.ADCSOC4CTL.bit.CHSEL = 0; // set SOC4 channel select to ADC1A0

Adc1Regs.ADCSOC5CTL.bit.CHSEL = 8; // set SOC5 channel select to ADC1B0

Adc1Regs.ADCSOC6CTL.bit.CHSEL = 4; // set SOC6 channel select to ADC1A4

Adc1Regs.ADCSOC7CTL.bit.CHSEL = 12; // set SOC7 channel select to ADC1B4

Adc1Regs.ADCSOC8CTL.bit.CHSEL = 0; // set SOC8 channel select to ADC1A0

Adc1Regs.ADCSOC9CTL.bit.CHSEL = 8; // set SOC9 channel select to ADC1B0

Adc1Regs.ADCSOC10CTL.bit.CHSEL = 4; // set SOC10 channel select to ADC1A4

Adc1Regs.ADCSOC11CTL.bit.CHSEL = 12; // set SOC11 channel select to ADC1B4

Adc1Regs.ADCSOC12CTL.bit.CHSEL = 0; // set SOC12 channel select to ADC1A0

Adc1Regs.ADCSOC13CTL.bit.CHSEL = 8; // set SOC13 channel select to ADC1B0

Adc1Regs.ADCSOC14CTL.bit.CHSEL = 4; // set SOC14 channel select to ADC1A4

Adc1Regs.ADCSOC15CTL.bit.CHSEL = 12; // set SOC15 channel select to ADC1B4

Adc1Regs.ADCSOC0CTL.bit.TRIGSEL = 5; // Set SOC0 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC1CTL.bit.TRIGSEL = 5; // set SOC1 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC2CTL.bit.TRIGSEL = 5; // Set SOC2 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC3CTL.bit.TRIGSEL = 5; // set SOC3 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC4CTL.bit.TRIGSEL = 5; // Set SOC4 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC5CTL.bit.TRIGSEL = 5; // set SOC5 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC6CTL.bit.TRIGSEL = 5; // Set SOC6 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC7CTL.bit.TRIGSEL = 5; // set SOC7 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC8CTL.bit.TRIGSEL = 5; // Set SOC8 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC9CTL.bit.TRIGSEL = 5; // set SOC9 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC10CTL.bit.TRIGSEL = 5; // Set SOC10 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC11CTL.bit.TRIGSEL = 5; // set SOC11 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC12CTL.bit.TRIGSEL = 5; // Set SOC12 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC13CTL.bit.TRIGSEL = 5; // set SOC13 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC14CTL.bit.TRIGSEL = 5; // Set SOC14 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC15CTL.bit.TRIGSEL = 5; // set SOC15 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC0CTL.bit.ACQPS = 6; // set SOC0 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC1CTL.bit.ACQPS = 6; // set SOC1 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC2CTL.bit.ACQPS = 6; // set SOC2 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC3CTL.bit.ACQPS = 6; // set SOC3 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC4CTL.bit.ACQPS = 6; // set SOC4 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC5CTL.bit.ACQPS = 6; // set SOC5 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC6CTL.bit.ACQPS = 6; // set SOC6 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC7CTL.bit.ACQPS = 6; // set SOC7 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC8CTL.bit.ACQPS = 6; // set SOC8 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC9CTL.bit.ACQPS = 6; // set SOC9 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC10CTL.bit.ACQPS = 6; // set SOC10 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC11CTL.bit.ACQPS = 6; // set SOC11 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC12CTL.bit.ACQPS = 6; // set SOC12 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC13CTL.bit.ACQPS = 6; // set SOC13 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC14CTL.bit.ACQPS = 6; // set SOC14 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC15CTL.bit.ACQPS = 6; // set SOC15 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

EDIS;

while(CpuTimer1Regs.TCR.bit.TIF==0); //This flag gets set when the CPU-timer decrements to zero, 100us

CpuTimer1Regs.TCR.bit.TIF = 1; // Writing a 1 to this bit clears the flag

POINTPULSE_DAT_REG = 1; // GPIO31– point pulse, point sanmple strat

//while((Adc1Regs.ADCCTL1.bit.ADCBSY !=0) ||(Adc1Regs.ADCCTL1.bit.ADCBSYCHN != 0x0f));

// 判断BUSY是否空闲,且最后一个通道是否是SOC15

while(Adc1Regs.ADCINTFLG.bit.ADCINT1==0); // 等待ADCINT1信号产生(由SOC15转换完毕产生)

Adc1Regs.ADCINTFLGCLR.bit.ADCINT1 = 1; // 清除ADCINT1中断信号

POINTPULSE_DAT_REG = 0; // high level width: 16 socs total time(include: Sample time + Conversion Time)

以上问题,多谢解答!

anfu lee:

对了!通过断点,观察ADC1Result0–ADC1Result15中的值,ADC1Result1以后的值不对,感觉好像SOC1完成后就中断了!但上面程序中明明是:

Adc1Regs.INTSEL1N2.bit.INT1SEL = 15; // setup ADC1 EOC15 to trigger ADCINT1

Adc1Regs.SOCPRICTL.bit.SOCPRIORITY = 15; // 15: SOC0-SOC14 are high priority, SOC15 is in round robin mode.

如果设置成 Adc1Regs.SOCPRICTL.bit.SOCPRIORITY = 16; // 16: All SOCs are in high priority mode, arbitrated by SOC number

也是一样一样的!

各位TI的大牛们,请解答一下下面的问题!

在我的设计中,ADC1采用overlap、依次顺序进行转换,各SOC0–SOC15均采用定时器TINT1的100us定时去触发,当SOC15转换完毕后去触发ADCINT1,ADCINT1在PIE中不允许中断,通过查询标记位判断16个SOC转换是否完成。在程序中在各步加设GIO置1或0的方式,通过示波器观察各步的执行时间和状态,发现采用查询ADCINT1中断标记位时,从ADC启动(通过TINT1启动)到ADC1 的中断标记置位时的时间间隔只有惊人的0.8us这么短,那可是16个SOC的转换啊!根据TI的SPRUH22F中P900到的参数,应该是543ns X 16=8.5us左右,差距是10倍左右!而采用查询ADCCTL1.bit.ADCBSY和ADCCTL1.bit.ADCBSYCHN方式,时间大约8us,较合理! ADCINT1和TINT1均允许中断,但在PIE中却不允许中断,通过查询方式,因中断和主程序在来回跳转时,也将消耗时间。

我的问题就是:如何通过查询相关的ADCINT1中断标记位,判断16个SOC转换是否完成?

以下是相关的程序代码,欢迎各位大牛们指教!谢谢! 硬件用的是Concerto F28M35xx controlCARD。软件是在\ti\controlSUITE\device_support\f28m36x\v206修改的。

EALLOW;

Adc1Regs.ADCCTL1.bit.ADCBGPWD = 1; // Power ADC1 BG, Bandgap circuit(带隙基准电路) 上电, 见TRM P911 ADCCTL1

Adc1Regs.ADCCTL1.bit.ADCREFPWD = 1; // Power reference,Reference buffers circuit power down

Adc1Regs.ADCCTL1.bit.ADCPWDN = 1; // Power ADC1, ADC power down

Adc1Regs.ADCCTL1.bit.ADCENABLE = 1; // Enable ADC1

Adc1Regs.ADCCTL1.bit.ADCREFSEL = 0; // Select interal BG, Internal/external reference select

Adc1Regs.ADCCTL2.bit.ADCNONOVERLAP = 0; // 0–Enable overlap mode

Adc1Regs.ADCCTL1.bit.INTPULSEPOS = 1; // ADCINT1 trips after AdcResults latch

Adc1Regs.INTSEL1N2.bit.INT1E = 1; // Enabled ADCINT1

Adc1Regs.INTSEL1N2.bit.INT1CONT = 0; // Disable ADCINT1 Continuous mode

Adc1Regs.INTSEL1N2.bit.INT1SEL = 15; // setup ADC1 EOC15 to trigger ADCINT1

Adc1Regs.SOCPRICTL.bit.SOCPRIORITY = 15; // 15: SOC0-SOC14 are high priority, SOC15 is in round robin mode.

AnalogSysctrlRegs.TRIG1SEL.all = 2; // Assigning TINT1 (CPU Timer 1) to ADC TRIGGER 1 of the ADC1 and ADC2 module

Adc1Regs.ADCSOC0CTL.bit.CHSEL = 0; // set SOC0 channel select to ADC1A0

Adc1Regs.ADCSOC1CTL.bit.CHSEL = 8; // set SOC1 channel select to ADC1B0

Adc1Regs.ADCSOC2CTL.bit.CHSEL = 4; // set SOC2 channel select to ADC1A4

Adc1Regs.ADCSOC3CTL.bit.CHSEL = 12; // set SOC3 channel select to ADC1B4

Adc1Regs.ADCSOC4CTL.bit.CHSEL = 0; // set SOC4 channel select to ADC1A0

Adc1Regs.ADCSOC5CTL.bit.CHSEL = 8; // set SOC5 channel select to ADC1B0

Adc1Regs.ADCSOC6CTL.bit.CHSEL = 4; // set SOC6 channel select to ADC1A4

Adc1Regs.ADCSOC7CTL.bit.CHSEL = 12; // set SOC7 channel select to ADC1B4

Adc1Regs.ADCSOC8CTL.bit.CHSEL = 0; // set SOC8 channel select to ADC1A0

Adc1Regs.ADCSOC9CTL.bit.CHSEL = 8; // set SOC9 channel select to ADC1B0

Adc1Regs.ADCSOC10CTL.bit.CHSEL = 4; // set SOC10 channel select to ADC1A4

Adc1Regs.ADCSOC11CTL.bit.CHSEL = 12; // set SOC11 channel select to ADC1B4

Adc1Regs.ADCSOC12CTL.bit.CHSEL = 0; // set SOC12 channel select to ADC1A0

Adc1Regs.ADCSOC13CTL.bit.CHSEL = 8; // set SOC13 channel select to ADC1B0

Adc1Regs.ADCSOC14CTL.bit.CHSEL = 4; // set SOC14 channel select to ADC1A4

Adc1Regs.ADCSOC15CTL.bit.CHSEL = 12; // set SOC15 channel select to ADC1B4

Adc1Regs.ADCSOC0CTL.bit.TRIGSEL = 5; // Set SOC0 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC1CTL.bit.TRIGSEL = 5; // set SOC1 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC2CTL.bit.TRIGSEL = 5; // Set SOC2 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC3CTL.bit.TRIGSEL = 5; // set SOC3 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC4CTL.bit.TRIGSEL = 5; // Set SOC4 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC5CTL.bit.TRIGSEL = 5; // set SOC5 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC6CTL.bit.TRIGSEL = 5; // Set SOC6 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC7CTL.bit.TRIGSEL = 5; // set SOC7 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC8CTL.bit.TRIGSEL = 5; // Set SOC8 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC9CTL.bit.TRIGSEL = 5; // set SOC9 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC10CTL.bit.TRIGSEL = 5; // Set SOC10 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC11CTL.bit.TRIGSEL = 5; // set SOC11 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC12CTL.bit.TRIGSEL = 5; // Set SOC12 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC13CTL.bit.TRIGSEL = 5; // set SOC13 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC14CTL.bit.TRIGSEL = 5; // Set SOC14 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC15CTL.bit.TRIGSEL = 5; // set SOC15 start trigger to ADC Trigger 1 of the ADC

Adc1Regs.ADCSOC0CTL.bit.ACQPS = 6; // set SOC0 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC1CTL.bit.ACQPS = 6; // set SOC1 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC2CTL.bit.ACQPS = 6; // set SOC2 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC3CTL.bit.ACQPS = 6; // set SOC3 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC4CTL.bit.ACQPS = 6; // set SOC4 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC5CTL.bit.ACQPS = 6; // set SOC5 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC6CTL.bit.ACQPS = 6; // set SOC6 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC7CTL.bit.ACQPS = 6; // set SOC7 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC8CTL.bit.ACQPS = 6; // set SOC8 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC9CTL.bit.ACQPS = 6; // set SOC9 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC10CTL.bit.ACQPS = 6; // set SOC10 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC11CTL.bit.ACQPS = 6; // set SOC11 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC12CTL.bit.ACQPS = 6; // set SOC12 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC13CTL.bit.ACQPS = 6; // set SOC13 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC14CTL.bit.ACQPS = 6; // set SOC14 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

Adc1Regs.ADCSOC15CTL.bit.ACQPS = 6; // set SOC15 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

EDIS;

while(CpuTimer1Regs.TCR.bit.TIF==0); //This flag gets set when the CPU-timer decrements to zero, 100us

CpuTimer1Regs.TCR.bit.TIF = 1; // Writing a 1 to this bit clears the flag

POINTPULSE_DAT_REG = 1; // GPIO31– point pulse, point sanmple strat

//while((Adc1Regs.ADCCTL1.bit.ADCBSY !=0) ||(Adc1Regs.ADCCTL1.bit.ADCBSYCHN != 0x0f));

// 判断BUSY是否空闲,且最后一个通道是否是SOC15

while(Adc1Regs.ADCINTFLG.bit.ADCINT1==0); // 等待ADCINT1信号产生(由SOC15转换完毕产生)

Adc1Regs.ADCINTFLGCLR.bit.ADCINT1 = 1; // 清除ADCINT1中断信号

POINTPULSE_DAT_REG = 0; // high level width: 16 socs total time(include: Sample time + Conversion Time)

以上问题,多谢解答!

mangui zhang:

回复 anfu lee:

应该有一个

State pointer吧

TI中文支持网

TI中文支持网