TI的工程师:您好,我买 了一个TI的LLC谐振开发套件,在controlsuite中找到了相应的程序,可是看不太懂,请问有没有该程序的解说手册,比如说程序流程图,程序控制策略的一些资料。我找的只是一个ti提供的《具有同步整流套件的高电压半桥线路电平控制(LLC)谐振DC/DC转换器软件》,里面只是讲述如何使用程序的步骤,并没有讲解程序的实质性内容。期待您的解答

rookiecalf:

没有,只有实验指导,理论知识你还是得掌握啊,要不咋研究

TI的工程师:您好,我买 了一个TI的LLC谐振开发套件,在controlsuite中找到了相应的程序,可是看不太懂,请问有没有该程序的解说手册,比如说程序流程图,程序控制策略的一些资料。我找的只是一个ti提供的《具有同步整流套件的高电压半桥线路电平控制(LLC)谐振DC/DC转换器软件》,里面只是讲述如何使用程序的步骤,并没有讲解程序的实质性内容。期待您的解答

Martin Yu:

在controlsuite中有该套件的硬件和软件手册的,有软件流程图等,对照看下程序还是比较清晰的;

C:\ti\controlSUITE\development_kits\TMDSHVRESLLCKIT_v1.0\~Docs

中文的应用笔记可以参考:

http://www.ti.com.cn/cn/lit/an/zhca540/zhca540.pdf

TI的工程师:您好,我买 了一个TI的LLC谐振开发套件,在controlsuite中找到了相应的程序,可是看不太懂,请问有没有该程序的解说手册,比如说程序流程图,程序控制策略的一些资料。我找的只是一个ti提供的《具有同步整流套件的高电压半桥线路电平控制(LLC)谐振DC/DC转换器软件》,里面只是讲述如何使用程序的步骤,并没有讲解程序的实质性内容。期待您的解答

xiaopu chen:

回复 rookiecalf:

谢谢解答

TI的工程师:您好,我买 了一个TI的LLC谐振开发套件,在controlsuite中找到了相应的程序,可是看不太懂,请问有没有该程序的解说手册,比如说程序流程图,程序控制策略的一些资料。我找的只是一个ti提供的《具有同步整流套件的高电压半桥线路电平控制(LLC)谐振DC/DC转换器软件》,里面只是讲述如何使用程序的步骤,并没有讲解程序的实质性内容。期待您的解答

xiaopu chen:

回复 Martin Yu:

非常感谢你为我解答,我想追问下:1用于构建3时候,后级同步整流的原理是什么样子的,检测I-SR是为了及时开通同步整流管,检测V-SR是为了整流管电压为零时,及时关断整流管吗? 我想问的是该方法的控制原理。

我想问的是该方法的控制原理。

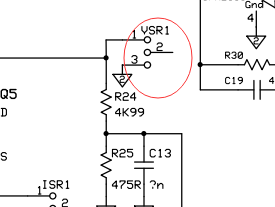

2原理图上的这种是什么意思? 红色圈出来的地方作用是什么,是测试点还是?

红色圈出来的地方作用是什么,是测试点还是?

期待您的解答,再次感谢。

TI的工程师:您好,我买 了一个TI的LLC谐振开发套件,在controlsuite中找到了相应的程序,可是看不太懂,请问有没有该程序的解说手册,比如说程序流程图,程序控制策略的一些资料。我找的只是一个ti提供的《具有同步整流套件的高电压半桥线路电平控制(LLC)谐振DC/DC转换器软件》,里面只是讲述如何使用程序的步骤,并没有讲解程序的实质性内容。期待您的解答

囧:

回复 xiaopu chen:

红色圈出来的地方只是预留的采样点,一般来说LLC都不会单独去采样SR电流,但是可以做保护,一般采样输出电流做环路就足够了。程序实际上并没有对SR的电流采样,程序中只做了电压环。

TI的工程师:您好,我买 了一个TI的LLC谐振开发套件,在controlsuite中找到了相应的程序,可是看不太懂,请问有没有该程序的解说手册,比如说程序流程图,程序控制策略的一些资料。我找的只是一个ti提供的《具有同步整流套件的高电压半桥线路电平控制(LLC)谐振DC/DC转换器软件》,里面只是讲述如何使用程序的步骤,并没有讲解程序的实质性内容。期待您的解答

xiaopu chen:

回复 囧:

谢谢您的回答,利用构建3的时候,这个套件采样采的SR电流吧?请问构建3与构建2相比,有点在哪里?

TI的工程师:您好,我买 了一个TI的LLC谐振开发套件,在controlsuite中找到了相应的程序,可是看不太懂,请问有没有该程序的解说手册,比如说程序流程图,程序控制策略的一些资料。我找的只是一个ti提供的《具有同步整流套件的高电压半桥线路电平控制(LLC)谐振DC/DC转换器软件》,里面只是讲述如何使用程序的步骤,并没有讲解程序的实质性内容。期待您的解答

囧:

回复 xiaopu chen:

Bulid Level2只是简单的完成了一个电压闭环的LLC频率控制,但是Build Level3在2的基础上加入了SR管的控制,使得SR的控制PWM下降沿跟随SR的电流变化,从而可以在SR电流到0点的时候再关段SR。

TI的工程师:您好,我买 了一个TI的LLC谐振开发套件,在controlsuite中找到了相应的程序,可是看不太懂,请问有没有该程序的解说手册,比如说程序流程图,程序控制策略的一些资料。我找的只是一个ti提供的《具有同步整流套件的高电压半桥线路电平控制(LLC)谐振DC/DC转换器软件》,里面只是讲述如何使用程序的步骤,并没有讲解程序的实质性内容。期待您的解答

xiaopu chen:

回复 囧:

谢谢您的回答,我追问如下:Comp1Regs.COMPCTL.bit.SYNCSEL = 1; // Sync with SYSCLK / use Qualification Comp1Regs.COMPCTL.bit.QUALSEL = 3; // Require input be stable for 3 consecutive SYSCLKs Comp1Regs.COMPCTL.bit.CMPINV = 1; // Output Low when true Comp1Regs.COMPCTL.bit.COMPSOURCE = 0; // Use internal DAC Comp1Regs.COMPCTL.bit.COMPDACEN = 1; // Enable DAC Comp1Regs.DACVAL.bit.DACVAL = COMP1; // Trip Current = DACVAL/1023*82.5

Comp2Regs.COMPCTL.bit.SYNCSEL = 1; // Sync with SYSCLK / use Qualification Comp2Regs.COMPCTL.bit.QUALSEL = 3; // Require input be stable for 3 consecutive SYSCLKs Comp2Regs.COMPCTL.bit.CMPINV = 1; // Output Low when true Comp2Regs.COMPCTL.bit.COMPSOURCE = 0; // Use internal DAC Comp2Regs.COMPCTL.bit.COMPDACEN = 1; // Enable DAC Comp2Regs.DACVAL.bit.DACVAL = COMP2; // Trip Current = DACVAL/1023*82.5

// Configure ePWM Digital Compare modules EPwm2Regs.DCTRIPSEL.bit.DCAHCOMPSEL = DC_COMP1OUT; // DCAH = Comparator 1 output EPwm2Regs.TZDCSEL.bit.DCAEVT1 = TZ_DCAH_LOW; // DCAEVT1 on DCAH low (will become active as Comparator1 output goes low), DCAL = don't care EPwm2Regs.DCACTL.bit.EVT1SRCSEL = DC_EVT_FLT; // DCAEVT1 filtered EPwm2Regs.DCACTL.bit.EVT1FRCSYNCSEL = DC_EVT_ASYNC; // Take async path EPwm2Regs.DCFCTL.bit.BLANKE = DC_BLANK_ENABLE; // Enable Blanking window EPwm2Regs.DCFCTL.bit.SRCSEL = DC_SRC_DCAEVT1; // Filter source = DCAEVT1 EPwm2Regs.DCFCTL.bit.PULSESEL = DC_PULSESEL_ZERO; // Filter start on TBCTR = ZERO EPwm2Regs.DCFOFFSET = 0; // Filter offset EPwm2Regs.DCFWINDOW = 0; // Blanking window duration

EPwm3Regs.DCTRIPSEL.bit.DCAHCOMPSEL = DC_COMP2OUT; // DCAH = Comparator 2 output EPwm3Regs.TZDCSEL.bit.DCAEVT1 = TZ_DCAH_LOW; // DCAEVT1 on DCAH low (will become active as Comparator2 output goes low), DCAL = don't care EPwm3Regs.DCACTL.bit.EVT1SRCSEL = DC_EVT_FLT; // DCAEVT1 filtered EPwm3Regs.DCACTL.bit.EVT1FRCSYNCSEL = DC_EVT_ASYNC; // Take async path EPwm3Regs.DCFCTL.bit.BLANKE = DC_BLANK_ENABLE; // Enable Blanking window EPwm3Regs.DCFCTL.bit.SRCSEL = DC_SRC_DCAEVT1; // Filter source = DCAEVT1 EPwm3Regs.DCFCTL.bit.PULSESEL = DC_PULSESEL_ZERO; // Filter start on TBCTR = ZERO EPwm3Regs.DCFOFFSET = 0; // Filter offset EPwm3Regs.DCFWINDOW = 0; // Blanking window duration

// Configure ePWM Trip-Zone module EPwm2Regs.TZCTL.bit.DCAEVT1 = TZ_FORCE_HI; // EPWM2A will go HIGH

EPwm3Regs.TZCTL.bit.DCAEVT1 = TZ_FORCE_HI; // EPWM3A will go HIGH

1.由以上程序可得,比较模块设的DCA基准为12V多一点,当采样过来的I-SR1值大于这个值得时候,比较输出值DC_comp1out为0。然后处罚TZ模块,使得EPMW2A输出为高,我这样理解对吗?

2.还有同步整流管开通后,如何做到当同步整流管中电流为0时候,让PWM为低电平,从而达到SR电流到0的时候关断SR的?

期待您的解答,再次感谢

TI的工程师:您好,我买 了一个TI的LLC谐振开发套件,在controlsuite中找到了相应的程序,可是看不太懂,请问有没有该程序的解说手册,比如说程序流程图,程序控制策略的一些资料。我找的只是一个ti提供的《具有同步整流套件的高电压半桥线路电平控制(LLC)谐振DC/DC转换器软件》,里面只是讲述如何使用程序的步骤,并没有讲解程序的实质性内容。期待您的解答

囧:

回复 xiaopu chen:

请参考以下我的回帖,注意比较器是设置输出反向,DC模块设置低有效触发TZ,所以只有电流超过DAC的设定值才会强制PWM出高,做到ZCS软开关

http://www.deyisupport.com/question_answer/microcontrollers/c2000/f/56/p/101042/267123.aspx#267123

TI中文支持网

TI中文支持网