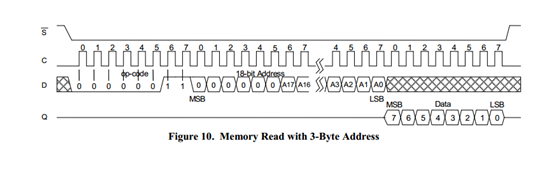

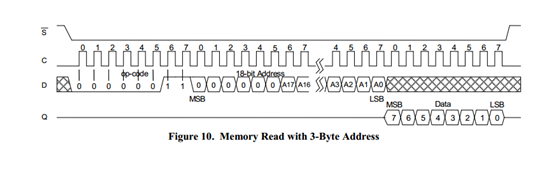

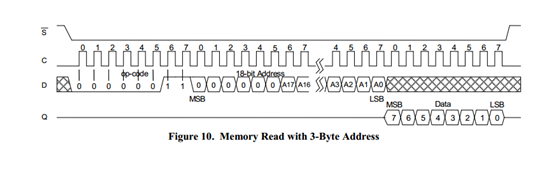

运用DSP对铁电RAM以SPI的方式进行读写操作,由于需要一次性发送多组8bit数据,时序图如图所示。

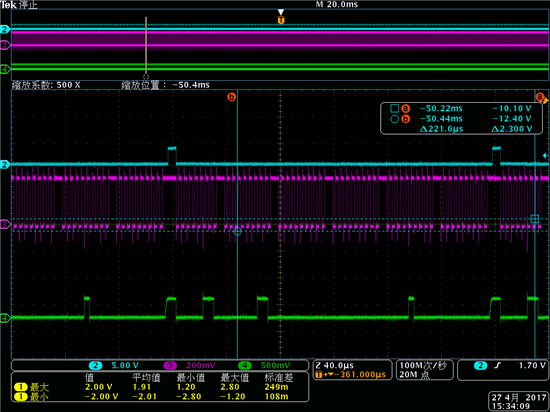

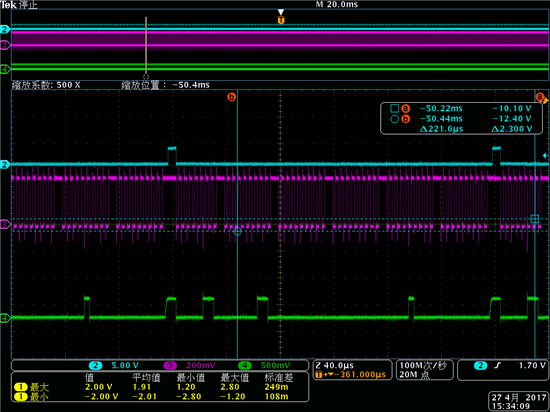

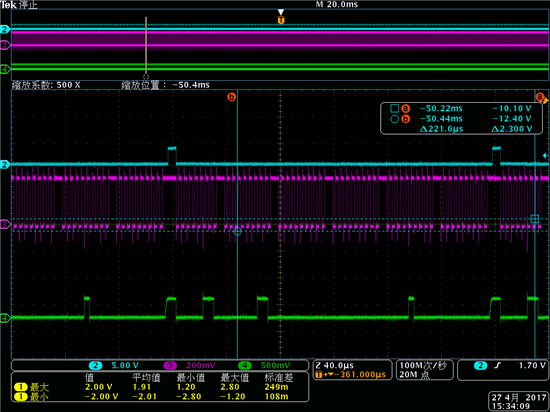

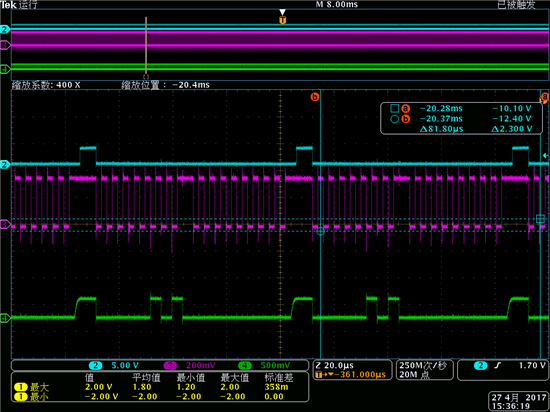

在运用28335中的McBSP配置为spi后,在时钟停止模式下,一次性发送6组8bit的数据,第一组数据的时钟个数正确,从第二组到第六组的时钟个数都不正确,如图所示。

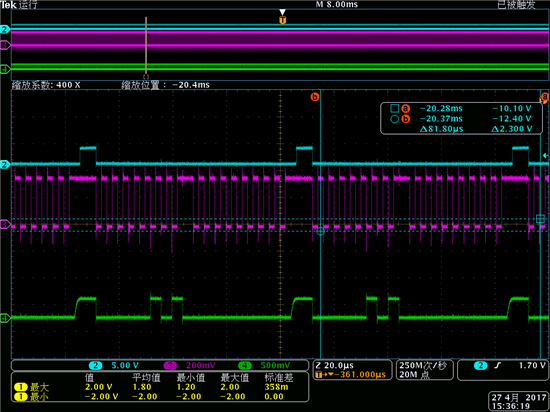

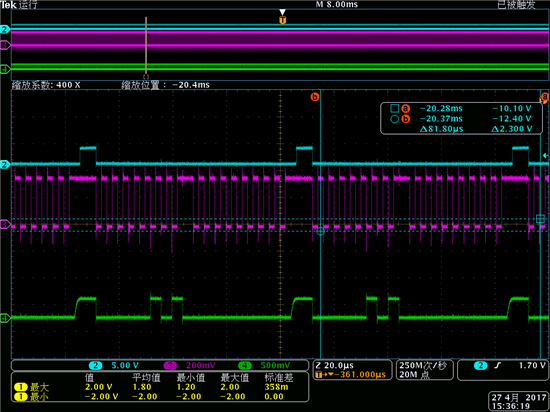

当改为每次发送2组数据之后,第2组数据的时钟也会多出一个,变成9个,如图。

初始化代码如下

void init_mcbsp_spi()

{// McBSP-A register settings

//step1McbspaRegs.SPCR2.bit.XRST=0;// Reset FS generator, sample rate generator & transmitter

McbspaRegs.SPCR1.bit.RRST=0;// Reset Receiver, Right justify word, Digital loopback dis.

//step2

McbspaRegs.SPCR2.bit.GRST=0;

//step3

McbspaRegs.SPCR1.bit.DLB = 0;

McbspaRegs.SPCR1.bit.CLKSTP = 2;// Together with CLKXP/CLKRP determines clocking scheme

//McbspaRegs.SPCR1.bit.DXENA = 1;

// McbspbRegs.SPCR1.bit.RJUST = 1;

//McbspaRegs.SPCR2.bit.XSYNCERR =1;

McbspaRegs.RCR1.bit.RFRLEN1 = 0;// rcv frame length is 1

McbspaRegs.RCR1.bit.RWDLEN1 = 0;//rcv word is 8bit

McbspaRegs.RCR2.bit.RDATDLY = 1;// FSX setup time 1 in master mode. 0 for slave mode (Receive)

McbspaRegs.RCR2.bit.RPHASE = 0;

McbspaRegs.RCR2.bit.RCOMPAND = 0;McbspaRegs.XCR1.bit.XFRLEN1=1;//frame length equal 6McbspaRegs.XCR1.bit.XWDLEN1=0;//transmit word is 8bitMcbspaRegs.XCR2.bit.XDATDLY=0;// FSX setup time 1 in master mode. 0 for slave mode (Transmit)McbspaRegs.XCR2.bit.XPHASE = 0;//McbspaRegs.XCR2.bit.XFIG = 0;// McbspaRegs.XCR2.bit.XCOMPAND =1;//McbspaRegs.SRGR1.bit.FWID = 150;McbspaRegs.SRGR1.bit.CLKGDV =150;McbspaRegs.SRGR2.bit.CLKSM = 1;McbspaRegs.SRGR2.bit.FSGM = 0;

McbspaRegs.SRGR2.bit.FPER = 0;

McbspaRegs.SRGR2.bit.GSYNC =1;

McbspaRegs.PCR.bit.FSXM = 1;

McbspaRegs.PCR.bit.FSRM = 0; //caution

McbspaRegs.PCR.bit.CLKXM = 1;

McbspaRegs.PCR.bit.CLKRM =0;

McbspaRegs.PCR.bit.SCLKME = 0;

McbspaRegs.PCR.bit.CLKXP = 1;// 1 means falling edge 0 means rising edge

McbspaRegs.PCR.bit.CLKRP = 0;

McbspaRegs.PCR.bit.FSXP = 1;

McbspaRegs.PCR.bit.FSRP = 1;//step4McbspaRegs.SPCR2.bit.GRST=1;// Enable the sample rate generator

delay_loop();// Wait at least 2 SRG clock cycles

//step5

McbspaRegs.SPCR2.bit.XRST=1;// Release TX from Reset

McbspaRegs.SPCR1.bit.RRST=1;// Release RX from Reset

delay_loop();

//step6McbspaRegs.SPCR2.bit.FRST=1;// Frame Sync Generator reset

}

发送代码如下

int send_data4[]={0x05,0x00};

int counter3 = 0;

for(counter3=0;counter3<=1;counter3++){ while(McbspaRegs.SPCR2.bit.XRDY !=1){} McbspaRegs.DXR1.all=send_data4[counter3]; if(McbspaRegs.SPCR1.bit.RRDY ==1) {tt = McbspaRegs.DRR1.all;}}

我仔细看了相关技术手册,在SPI模式下有诸多规定,即使一步步按照这些规定来配置寄存器也没有消除这个问题,已经困扰一个月了,我觉得是能配置成功的,求各位专家为我指点指点!

BOWEN ZHOU:

求各位专家给我指点指点~=~

运用DSP对铁电RAM以SPI的方式进行读写操作,由于需要一次性发送多组8bit数据,时序图如图所示。

在运用28335中的McBSP配置为spi后,在时钟停止模式下,一次性发送6组8bit的数据,第一组数据的时钟个数正确,从第二组到第六组的时钟个数都不正确,如图所示。

当改为每次发送2组数据之后,第2组数据的时钟也会多出一个,变成9个,如图。

初始化代码如下

void init_mcbsp_spi()

{// McBSP-A register settings

//step1McbspaRegs.SPCR2.bit.XRST=0;// Reset FS generator, sample rate generator & transmitter

McbspaRegs.SPCR1.bit.RRST=0;// Reset Receiver, Right justify word, Digital loopback dis.

//step2

McbspaRegs.SPCR2.bit.GRST=0;

//step3

McbspaRegs.SPCR1.bit.DLB = 0;

McbspaRegs.SPCR1.bit.CLKSTP = 2;// Together with CLKXP/CLKRP determines clocking scheme

//McbspaRegs.SPCR1.bit.DXENA = 1;

// McbspbRegs.SPCR1.bit.RJUST = 1;

//McbspaRegs.SPCR2.bit.XSYNCERR =1;

McbspaRegs.RCR1.bit.RFRLEN1 = 0;// rcv frame length is 1

McbspaRegs.RCR1.bit.RWDLEN1 = 0;//rcv word is 8bit

McbspaRegs.RCR2.bit.RDATDLY = 1;// FSX setup time 1 in master mode. 0 for slave mode (Receive)

McbspaRegs.RCR2.bit.RPHASE = 0;

McbspaRegs.RCR2.bit.RCOMPAND = 0;McbspaRegs.XCR1.bit.XFRLEN1=1;//frame length equal 6McbspaRegs.XCR1.bit.XWDLEN1=0;//transmit word is 8bitMcbspaRegs.XCR2.bit.XDATDLY=0;// FSX setup time 1 in master mode. 0 for slave mode (Transmit)McbspaRegs.XCR2.bit.XPHASE = 0;//McbspaRegs.XCR2.bit.XFIG = 0;// McbspaRegs.XCR2.bit.XCOMPAND =1;//McbspaRegs.SRGR1.bit.FWID = 150;McbspaRegs.SRGR1.bit.CLKGDV =150;McbspaRegs.SRGR2.bit.CLKSM = 1;McbspaRegs.SRGR2.bit.FSGM = 0;

McbspaRegs.SRGR2.bit.FPER = 0;

McbspaRegs.SRGR2.bit.GSYNC =1;

McbspaRegs.PCR.bit.FSXM = 1;

McbspaRegs.PCR.bit.FSRM = 0; //caution

McbspaRegs.PCR.bit.CLKXM = 1;

McbspaRegs.PCR.bit.CLKRM =0;

McbspaRegs.PCR.bit.SCLKME = 0;

McbspaRegs.PCR.bit.CLKXP = 1;// 1 means falling edge 0 means rising edge

McbspaRegs.PCR.bit.CLKRP = 0;

McbspaRegs.PCR.bit.FSXP = 1;

McbspaRegs.PCR.bit.FSRP = 1;//step4McbspaRegs.SPCR2.bit.GRST=1;// Enable the sample rate generator

delay_loop();// Wait at least 2 SRG clock cycles

//step5

McbspaRegs.SPCR2.bit.XRST=1;// Release TX from Reset

McbspaRegs.SPCR1.bit.RRST=1;// Release RX from Reset

delay_loop();

//step6McbspaRegs.SPCR2.bit.FRST=1;// Frame Sync Generator reset

}

发送代码如下

int send_data4[]={0x05,0x00};

int counter3 = 0;

for(counter3=0;counter3<=1;counter3++){ while(McbspaRegs.SPCR2.bit.XRDY !=1){} McbspaRegs.DXR1.all=send_data4[counter3]; if(McbspaRegs.SPCR1.bit.RRDY ==1) {tt = McbspaRegs.DRR1.all;}}

我仔细看了相关技术手册,在SPI模式下有诸多规定,即使一步步按照这些规定来配置寄存器也没有消除这个问题,已经困扰一个月了,我觉得是能配置成功的,求各位专家为我指点指点!

user5799618:

回复 BOWEN ZHOU:

可以加个QQ好友讨论下吗1204918053

运用DSP对铁电RAM以SPI的方式进行读写操作,由于需要一次性发送多组8bit数据,时序图如图所示。

在运用28335中的McBSP配置为spi后,在时钟停止模式下,一次性发送6组8bit的数据,第一组数据的时钟个数正确,从第二组到第六组的时钟个数都不正确,如图所示。

当改为每次发送2组数据之后,第2组数据的时钟也会多出一个,变成9个,如图。

初始化代码如下

void init_mcbsp_spi()

{// McBSP-A register settings

//step1McbspaRegs.SPCR2.bit.XRST=0;// Reset FS generator, sample rate generator & transmitter

McbspaRegs.SPCR1.bit.RRST=0;// Reset Receiver, Right justify word, Digital loopback dis.

//step2

McbspaRegs.SPCR2.bit.GRST=0;

//step3

McbspaRegs.SPCR1.bit.DLB = 0;

McbspaRegs.SPCR1.bit.CLKSTP = 2;// Together with CLKXP/CLKRP determines clocking scheme

//McbspaRegs.SPCR1.bit.DXENA = 1;

// McbspbRegs.SPCR1.bit.RJUST = 1;

//McbspaRegs.SPCR2.bit.XSYNCERR =1;

McbspaRegs.RCR1.bit.RFRLEN1 = 0;// rcv frame length is 1

McbspaRegs.RCR1.bit.RWDLEN1 = 0;//rcv word is 8bit

McbspaRegs.RCR2.bit.RDATDLY = 1;// FSX setup time 1 in master mode. 0 for slave mode (Receive)

McbspaRegs.RCR2.bit.RPHASE = 0;

McbspaRegs.RCR2.bit.RCOMPAND = 0;McbspaRegs.XCR1.bit.XFRLEN1=1;//frame length equal 6McbspaRegs.XCR1.bit.XWDLEN1=0;//transmit word is 8bitMcbspaRegs.XCR2.bit.XDATDLY=0;// FSX setup time 1 in master mode. 0 for slave mode (Transmit)McbspaRegs.XCR2.bit.XPHASE = 0;//McbspaRegs.XCR2.bit.XFIG = 0;// McbspaRegs.XCR2.bit.XCOMPAND =1;//McbspaRegs.SRGR1.bit.FWID = 150;McbspaRegs.SRGR1.bit.CLKGDV =150;McbspaRegs.SRGR2.bit.CLKSM = 1;McbspaRegs.SRGR2.bit.FSGM = 0;

McbspaRegs.SRGR2.bit.FPER = 0;

McbspaRegs.SRGR2.bit.GSYNC =1;

McbspaRegs.PCR.bit.FSXM = 1;

McbspaRegs.PCR.bit.FSRM = 0; //caution

McbspaRegs.PCR.bit.CLKXM = 1;

McbspaRegs.PCR.bit.CLKRM =0;

McbspaRegs.PCR.bit.SCLKME = 0;

McbspaRegs.PCR.bit.CLKXP = 1;// 1 means falling edge 0 means rising edge

McbspaRegs.PCR.bit.CLKRP = 0;

McbspaRegs.PCR.bit.FSXP = 1;

McbspaRegs.PCR.bit.FSRP = 1;//step4McbspaRegs.SPCR2.bit.GRST=1;// Enable the sample rate generator

delay_loop();// Wait at least 2 SRG clock cycles

//step5

McbspaRegs.SPCR2.bit.XRST=1;// Release TX from Reset

McbspaRegs.SPCR1.bit.RRST=1;// Release RX from Reset

delay_loop();

//step6McbspaRegs.SPCR2.bit.FRST=1;// Frame Sync Generator reset

}

发送代码如下

int send_data4[]={0x05,0x00};

int counter3 = 0;

for(counter3=0;counter3<=1;counter3++){ while(McbspaRegs.SPCR2.bit.XRDY !=1){} McbspaRegs.DXR1.all=send_data4[counter3]; if(McbspaRegs.SPCR1.bit.RRDY ==1) {tt = McbspaRegs.DRR1.all;}}

我仔细看了相关技术手册,在SPI模式下有诸多规定,即使一步步按照这些规定来配置寄存器也没有消除这个问题,已经困扰一个月了,我觉得是能配置成功的,求各位专家为我指点指点!

mangui zhang:

是不是与MCU McBSP 16bit有关系 下面供参考 mcbsp配置成spi —————————————————–mcbsp—————————————————————————————- void LAN1_Gpio(void) { //mcbspb 做spi, EALLOW; GpioCtrlRegs.GPAPUD.bit.GPIO24 = 0; // Enable pull-up on GPIO24 (SPISIMO) GpioCtrlRegs.GPAPUD.bit.GPIO25 = 0; // Enable pull-up on GPIO25 (SPISOMI) GpioCtrlRegs.GPAPUD.bit.GPIO26 = 0; // Enable pull-up on GPIO26 (***) GpioCtrlRegs.GPAQSEL2.bit.GPIO24 = 3; // Asynch input GPIO24 (SPISIMO) GpioCtrlRegs.GPAQSEL2.bit.GPIO25 = 3; // Asynch input GPIO25 (SPISOMI) GpioCtrlRegs.GPAQSEL2.bit.GPIO26 = 3; // Asynch input GPIO26 (***) GpioCtrlRegs.GPAQSEL2.bit.GPIO27 = 3; // Asynch input GPIO27 (SPISTE) //下面的值是3 GpioCtrlRegs.GPAMUX2.bit.GPIO24 = 3; // Configure GPIO24 as SPISIMO GpioCtrlRegs.GPAMUX2.bit.GPIO25 = 3; // Configure GPIO25 as SPISOMI GpioCtrlRegs.GPAMUX2.bit.GPIO26 = 3; // Configure GPIO26 as *** //Configure GPIO49 as RESET GpioCtrlRegs.GPBPUD.bit.GPIO49 = 0;// Enable pullup GpioDataRegs.GPBSET.bit.GPIO49 = 1; // Load output latch GpioCtrlRegs.GPBMUX2.bit.GPIO49 = 0; // GpioCtrlRegs.GPBDIR.bit.GPIO49 = 1; // GPIO49 = output //Configure GPIO27 as SPISTEA GpioCtrlRegs.GPAPUD.bit.GPIO27 = 0;// Enable pullup GpioDataRegs.GPASET.bit.GPIO27 = 1; // Load output latch GpioCtrlRegs.GPAMUX2.bit.GPIO27 = 0; // GpioCtrlRegs.GPADIR.bit.GPIO27 = 1; // GPIO27 = output EDIS; }123456789101112131415161718192021222324252627282930313233343536 #define RD =1;//编译控制字根据自己的芯片进行选择 void LAN1_Init() { // McBSP register settings McbspbRegs.SPCR2.all=0x0000; // Reset FS generator, sample rate generator & transmitter McbspbRegs.SPCR1.all=0x0000; // Reset Receiver, Right justify word, Digital loopback dis. McbspbRegs.PCR.all=0x0F08; //(CLKXM=CLKRM=FSXM=FSRM= 1, FSXP = 1) McbspbRegs.SPCR1.bit.DLB = 0; McbspbRegs.PCR.bit.CLKXM = 1; McbspbRegs.PCR.bit.CLKRM = 1; McbspbRegs.PCR.bit.SCLKME = 0;//SCLKME = 0,CLKSM =1,选择LSPCLK时钟源 McbspbRegs.SRGR2.bit.CLKSM = 1; McbspbRegs.SRGR2.bit.FPER = 1;// McbspbRegs.PCR.bit.FSRM = 1;//接收帧同步模式 McbspbRegs.SRGR1.bit.CLKGDV = 1; // Frame Width = 1 ,CLKG period,一分频2017.12.29 McbspbRegs.SRGR1.bit.FWID = 0; // Frame Width = 1 CLKG period #if RND McbspbRegs.SPCR1.bit.CLKSTP = 2; // Together with CLKXP/CLKRP determines clocking scheme McbspbRegs.PCR.bit.CLKXP = 0; // CPOL = 0, CPHA = 0 McbspbRegs.PCR.bit.CLKRP = 0; #endif #if RD McbspbRegs.SPCR1.bit.CLKSTP = 3; // Together with CLKXP/CLKRP determines clocking scheme McbspbRegs.PCR.bit.CLKXP = 0; // CPOL = 0, CPHA = 1 McbspbRegs.PCR.bit.CLKRP = 1; #endif #if FND McbspbRegs.SPCR1.bit.CLKSTP = 2; // Together with CLKXP/CLKRP determines clocking scheme McbspbRegs.PCR.bit.CLKXP = 1; // CPOL = 1, CPHA = 0 McbspbRegs.PCR.bit.CLKRP = 0; #endif #if FD McbspbRegs.SPCR1.bit.CLKSTP = 3; // Together with CLKXP/CLKRP determines clocking scheme McbspbRegs.PCR.bit.CLKXP = 1; // CPOL = 1, CPHA = 1 McbspbRegs.PCR.bit.CLKRP = 1; #endif McbspbRegs.RCR2.all=0x0001; // Single-phase frame, 1 word/frame, No companding (Receive) McbspbRegs.RCR1.all=0x0000; // Default 8-bits per word. Note, phase 2 bits should be ignored. McbspbRegs.XCR2.all=0x0001; // Single-phase frame, 1 word/frame, No companding (Transmit) McbspbRegs.XCR1.all=0x0000; // Default 8-bits per word. Note, phase 2 bits should be ignored. McbspbRegs.SRGR2.all=0x2000; // CLKSM=1, FPER = 2^6 CLKG periods McbspbRegs.SRGR1.all=0x000F; // Frame Width = 1 CLKG period, CLKGDV=2 McbspbRegs.SPCR1.bit.DXENA=1; McbspbRegs.SPCR2.bit.XINTM = 0; McbspbRegs.SPCR1.bit.RINTM = 0; McbspbRegs.MFFINT.bit.RINT = 0; McbspbRegs.XCR2.bit.XDATDLY = 1;//1位延迟位,stop mode 必须置1 McbspbRegs.RCR2.bit.RDATDLY = 1;//1位延迟位,stop mode 必须置1 McbspbRegs.RCR1.bit.RWDLEN1=0; // 16-bit word McbspbRegs.XCR1.bit.XWDLEN1=0; // 16-bit word delay_loop(); McbspbRegs.SPCR2.all |=0x00C1; // Frame sync & sample rate generators pulled out of reset McbspbRegs.SPCR2.bit.FRST=1; // Frame Sync Generator reset McbspbRegs.SPCR2.bit.XRST=1; // Enable Transmitter McbspbRegs.SPCR1.bit.RRST=1; // Enable Receiver }

TI中文支持网

TI中文支持网