至TI的老司机!

请问28335的中断优先级可以软件配置吗?

我在网上看到的帖子说在DSP281x_SWPrioritizedIsrLevels.h文件里可以改变外设的中断优先级,但我试了,貌似不成功!!!

mangui zhang:

不可设置 可以嵌套

至TI的老司机!

请问28335的中断优先级可以软件配置吗?

我在网上看到的帖子说在DSP281x_SWPrioritizedIsrLevels.h文件里可以改变外设的中断优先级,但我试了,貌似不成功!!!

z fang:

回复 mangui zhang:

我在工程中开了两个中断,一个timer0,另一个ePWM1的ePWM1_INT零点中断;

系统默认的中断优先级是timer0为5(周期1mS), ePWM1_INT的优先级为7(周期200uS),ePWM1_INT的中断会被timer0 的中断打乱;

我希望实现的是ePWM1_INT的中断处理过程不被timer0的中断打断,ePWM1_INT进中断的时间严格控制为200uS。(如果可以改变他们的优先级就很容易实现)

中断嵌套应该不能实现目的吧?

谢谢!

至TI的老司机!

请问28335的中断优先级可以软件配置吗?

我在网上看到的帖子说在DSP281x_SWPrioritizedIsrLevels.h文件里可以改变外设的中断优先级,但我试了,貌似不成功!!!

10#:

回复 z fang:

默认情况下C28x的中断是不嵌套的,所以理论上不可能出现EPWM1的中断被Timer0打断的情况。

但是按照你的描述,有可能会出现这两个中断刚好同时触发,那么此时更高优先级的中断会响应,因此就可能出现EPWM1的中断需要等Timer0的中断执行完成以后才可能被响应,比如,假设它们完全同时计时,在EPWM1的第5个中断发生时,Timer0的中断也发生,就会出现这种情况。

如果是这种情况,那么建议让EPWM1先计数,然后才让Timer0计数,就会使它们的中断触发点错开,从而每次EPWM1的中断都能响应。

另一种办法是使用一个更低优先级的EPWM或者Timer来实现,比如没有使用到的EPWM5,或者Timer1和2,都能保证EPWM1被及时响应。

至TI的老司机!

请问28335的中断优先级可以软件配置吗?

我在网上看到的帖子说在DSP281x_SWPrioritizedIsrLevels.h文件里可以改变外设的中断优先级,但我试了,貌似不成功!!!

z fang:

回复 10#:

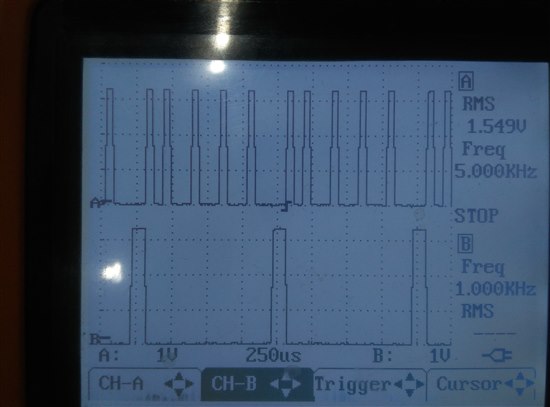

确实像您说的,下图中上面部分为ePWM1的零点中断响应,下边部分为timer0的中断响应,ePWM的中断响应很明显被延后了!

既然不能改,我就不去折腾了!!

至TI的老司机!

请问28335的中断优先级可以软件配置吗?

我在网上看到的帖子说在DSP281x_SWPrioritizedIsrLevels.h文件里可以改变外设的中断优先级,但我试了,貌似不成功!!!

Igor An:

回复 z fang:

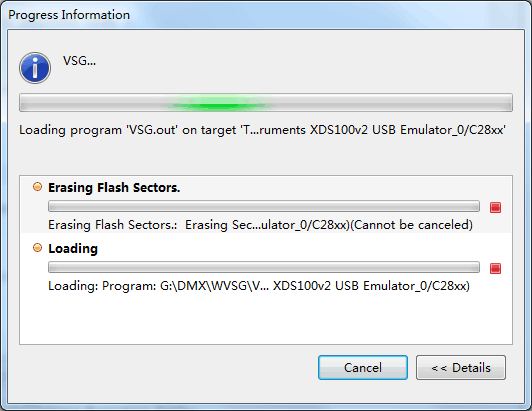

C2000的中断是可以通过软件实现嵌套,如下面例子:

interrupt mainISR(void)

{

volatile Uint16 TempPIEIER = PieCtrlRegs.PIEIER1.all;

IER |= M_INT1; IER &= M_INT1; PieCtrlRegs.PIEIER1.all &= 0x01; // Only allow ADCINT1 to interrupt PieCtrlRegs.PIEACK.all = 0xFFFF;

EINT;

// User code begin

//……

//User code end

DINT; AdcRegs.ADCINTFLGCLR.all = 0x2; //Clear interrupt flag; PieCtrlRegs.PIEIER1.all = TempPIEIER;

}

在进中断服务函数后,立即把想要允许的中断源所在组的IER,PIEIER清除,即在中断函数内,专门赋值一个被允许的中断源配置。在这之前,用变量存储进中断之前的中断配置,即如例子中的第一句“volatile Uint16 TempPIEIER = PieCtrlRegs.PIEIER1.all;”, 在出中断时再赋回去。

至TI的老司机!

请问28335的中断优先级可以软件配置吗?

我在网上看到的帖子说在DSP281x_SWPrioritizedIsrLevels.h文件里可以改变外设的中断优先级,但我试了,貌似不成功!!!

10#:

回复 z fang:

建议仍然是使用不同的EPWM或者Timer,中断优先级比EPWM1的。

@Igor,嵌套只能是高优先级的中断打断低优先级的,而现在他的问题是同时发生时,Timer0中断比EPWM1中断先响应了。

至TI的老司机!

请问28335的中断优先级可以软件配置吗?

我在网上看到的帖子说在DSP281x_SWPrioritizedIsrLevels.h文件里可以改变外设的中断优先级,但我试了,貌似不成功!!!

Igor An:

回复 10#:

恩,是的。

如果有可能,最好考虑是否能让两个中断发生的时刻错开,避免同时产生中断事件,实在避不开再考虑优先级排序及嵌套处理。

至TI的老司机!

请问28335的中断优先级可以软件配置吗?

我在网上看到的帖子说在DSP281x_SWPrioritizedIsrLevels.h文件里可以改变外设的中断优先级,但我试了,貌似不成功!!!

z fang:

回复 10#:

我重新改用了timer1的中断,它的优先级比ePWM1_INT低,但做出来的效果是这样的:

图中A的波形是timer1产生的中断里拉高GPIO,延时了大概100uS再拉低(周期为1000uS);

图中B的波形是ePWM1_INT中断里将另一个GPIO脚拉高,延时150uS再拉低,从B的波形可以看出,1、2个脉冲产生的时间是没问题的,但第3个脉冲本该在箭头所指的时间就产生,但这一时刻timer1的中断处理还没结束,第三个脉冲等到了timer1的中断处理结束后才进入的;

问题是,为什么优先级更高的ePWM1_INT没有打断低优先级的timer1,而是等到它处理结束了才进中断?这是怎么回事呢?

后面附上两个中断的代码:

interrupt void EPWM1_INT_ISR(void) // EPWM-1{ static unsigned int ePWMIntCunt = 0;

EPwm1Regs.ETCLR.bit.INT = 1; IER |= M_INT3;

GpioDataRegs.GPADAT.bit.GPIO12 = 1; ePWMIntCunt +=1; DELAY_US(150); GpioDataRegs.GPADAT.bit.GPIO12 = 0;

// To receive more interrupts from this PIE group, acknowledge this interrupt PieCtrlRegs.PIEACK.all = PIEACK_GROUP3;

}

interrupt void INT13_ISR(void) // INT13 or CPU-Timer1{ int i = 1000; // Insert ISR Code here

CpuTimer1.InterruptCount +=1; GpioDataRegs.GPADAT.bit.GPIO13 = 1;// DELAY_US(50); while(i>0){ i–; } GpioDataRegs.GPADAT.bit.GPIO13 = 0;

}

至TI的老司机!

请问28335的中断优先级可以软件配置吗?

我在网上看到的帖子说在DSP281x_SWPrioritizedIsrLevels.h文件里可以改变外设的中断优先级,但我试了,貌似不成功!!!

z fang:

回复 10#:

哦!!

搞定,搞定……

谢谢!!

TI中文支持网

TI中文支持网