问题背景:

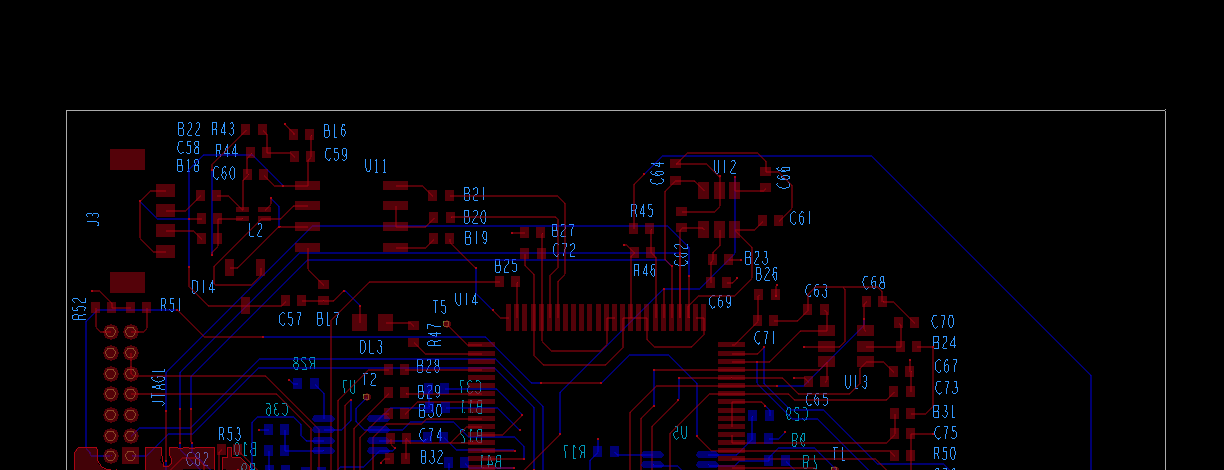

参考AM3358的EVM(TMDSSK3358 )官方的开发板设计了一块新硬件系统,新设计的硬件系统只是外设裁剪了一些,内存以及电源管理芯片等都是保持和EVM官方开发板一致。

该硬件系统uboot已经验证通过(uboot2015.7),内核测试正常

问题:考虑成本,目前使用AM3352BZCZA60来代替AM3358,其他不变。然后使用串口加载编译好的uboot,发现加载SPL死机。后面按照下文修改uboot,重新加载SPL

问题分析:

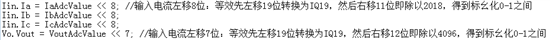

SPL软件流程 --start.s 主要是CPU的中断设置,关闭MMU等 --调用lowlevel_init.S 禁止看门狗 初始化相关的UART --crt0.S调用_main函数 该文件调用一个重要的函数 board_init_f函数: 1.board_early_init_f();//初始化时钟树 PLL 主要设置了MPU的频率为300MHZ 设置内核频率输出200MHZ/250MHZ 设置DDR的输出时钟为303MHZ,注意DDR PLL 的输入参考时钟源来至外部晶振 时钟树的关系--- |OSC|外部24MHZ ---||------------------------------------------------||| -------------------------- |DPLL_CORE||DPLL_MPU|| DPLL_DDR| -------------------------- 2.sdram_init(); //初始化 DDR, 这个函数初始化SDRAM 注意: 初始化SDRAM完成之后,才会通过函数am335x_get_efuse_mpu_max_freq(cdev)来读取 efuse_sma 寄存器的低 13 位来判别芯片 MPU 的最大频率 Fmax,。

接着初始化 PMIC,使得芯片工作电压满足最高频率 。 最后设置 Core 频率=1G 和 Mpu 最大频率 Fmax,am3352返回最大的频率为600MHZ, 从上述描述可以知道,SDRAM和MPU之间的没有关系以及时钟之间也没有关系,因为MPU一开始都是设置为300MHZ的频率,

设置为最高的工作频率是在SDRAM后面开始设置的 调试的时候: 在sdram_init后面加入内存检查函数

uint *start_addr = (uint *)0x80000000;

uint *src_start_addr = (uint *)0x80000000;

int i;

uint tmpdata;

for(i = 0; i < 10; i++)

{

*(start_addr++) = i;

}

for(i=0; i < 10; i ++)

{

tmpdata = *(src_start_addr ++);

if(tmpdata != i)

{

debug_voip(100);//指示灯闪烁 快 (错误状态)

}

}

while(1) //停止在这里

debug_voip(3000);//指示灯闪烁 慢

将上面的SPL程序烧录到老版本的硬件板子,程序运行正常(不会进入到快闪烁指示),

然后将程序烧录到新的硬件中,进入错误状态

总结:因为内存电路包括内存芯片这一块完全相同,电源都测试过,都正常,并且程序都只运行到SDRAM初始化阶段,理论上烧录同一块SPL代码,

都会进入到正常状态

请教的问题:

AM3352和AM3358是否完全兼容???

上面的问题分析是否有误???

Steven Liu1:

用一个链接track就可以了,简单来说,在确认了你的DDR3最初的配置是没问题的情况下,你的上述逻辑都是正确的。

http://www.deyisupport.com/question_answer/dsp_arm/sitara_arm/f/25/t/122699.aspx

TI中文支持网

TI中文支持网