我想请教下一个我在开发过程中遇到的问题:

关于用F28335McBSP模拟spi收发数据,配置mcbspB成SPI模式,从模式和上位机通信,每次接收和发送数据长度为8位。上位机那边发出36×8位的数据(头两个八位数据为帧头0XAA和指令0X5A),dsp返回一些计算后的数据,采用如下代码(简化逻辑后的)。

for(j=0;j<36;j++) //Initialize data { S_data[j]=0; } while(1) //keep running:send data { for(m=0;m<36;m++)

{

McbspbRegs.DXR1.all = S_data[m];

while(McbspbRegs.SPCR1.bit.RRDY == 0 ) { } flagdate = McbspbRegs.DRR1.all; }

for(j=0;j<36;j++) //change send data { S_data[j]++; } }

但是根据示波器的结果观察看,dsp发出的数据不对,对应输入的36个数据,dsp发出的为:

S_data[35] S_data[0] S_data[1] S_data[2]…S_data[34]然后接收下一组36个数据,发出的还是这个顺序。

能够知道的是,S_data[35] 为上一周期数据的最后一个8位,不知道为什么会有延迟。

我这样的代码,逻辑上有问题吗,还是说寄存器的配置问题,我是设置的8位数据发送,36个字,对应寄存器设置如下:

void InitMcbspb(void)

{

// reset McBSP and SRG

McbspbRegs.SPCR2.bit.FRST=0;

McbspbRegs.SPCR2.bit.GRST=0;

McbspbRegs.SPCR2.bit.XRST=0;

McbspbRegs.SPCR1.bit.RRST=0;

// SPI mode

McbspbRegs.SPCR1.bit.DLB = 0;

McbspbRegs.SPCR1.bit.CLKSTP = 2;

// clock set as slave mode

McbspbRegs.PCR.bit.SCLKME = 0;

McbspbRegs.SRGR2.bit.CLKSM = 1;

// McbspbRegs.PCR.bit.CLKRM = 1;

McbspbRegs.PCR.bit.CLKXM = 0;

McbspbRegs.PCR.bit.CLKRP = 0; //jdp

McbspbRegs.PCR.bit.CLKXP = 0;

McbspbRegs.SRGR1.bit.CLKGDV = 1;

// FSG set as slave mode

//McbspbRegs.PCR.bit.FSRM = 0; //jdp

McbspbRegs.PCR.bit.FSXM = 0;

//McbspbRegs.PCR.bit.FSRP = 1; //jdp

McbspbRegs.PCR.bit.FSXP = 1;

//McbspbRegs.RCR2.bit.RDATDLY= 0;

//McbspbRegs.XCR2.bit.XDATDLY= 0;

// enable McBSP

delay_loop();

McbspbRegs.SPCR2.bit.GRST = 1;

clkg_delay_loop();

McbspbRegs.SPCR2.bit.XRST = 1;

McbspbRegs.SPCR1.bit.RRST = 1;

McbspbRegs.SPCR2.bit.FRST = 1;

}

void InitMcbspb8bit(void)

{

McbspbRegs.RCR1.bit.RFRLEN1=35; // 36-word

McbspbRegs.RCR1.bit.RWDLEN1=0; // 8-bit

McbspbRegs.XCR1.bit.XFRLEN1=35; // 8 word

McbspbRegs.XCR1.bit.XWDLEN1=0; // 8-bit

}

调了很久了,不论怎么设置寄存器和更改代码逻辑,都会有1~3个数据(每个数据8位)的延迟。

各位能帮我看看是哪里存在的问题吗?多谢了哈~

ps:

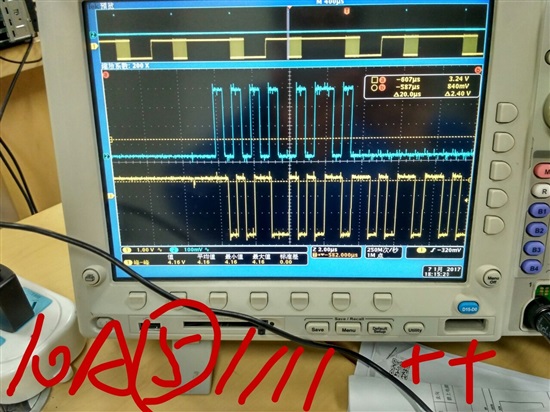

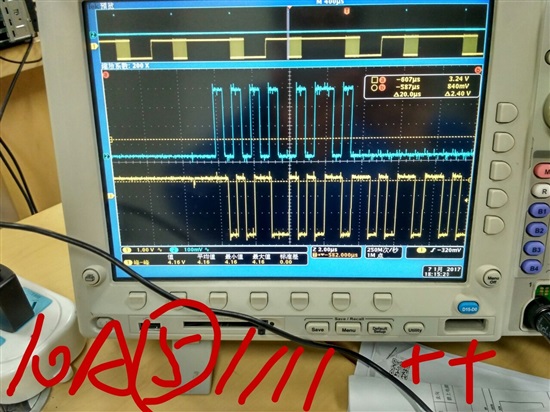

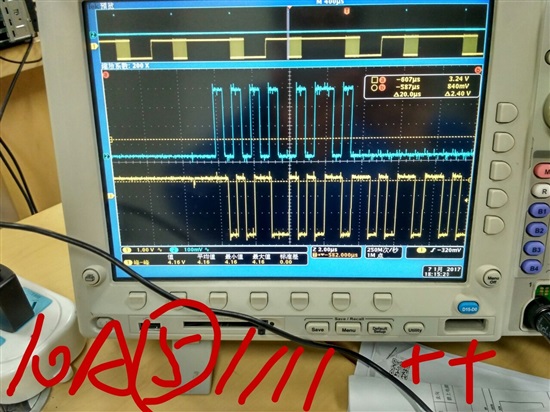

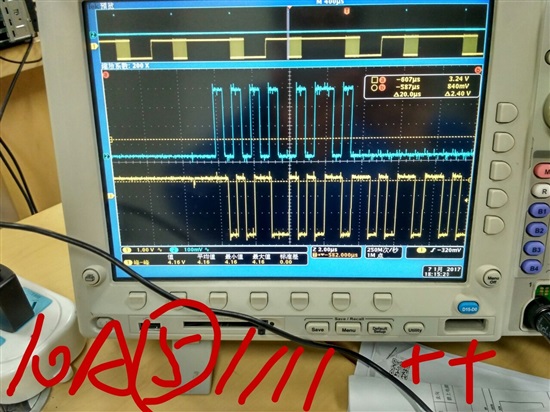

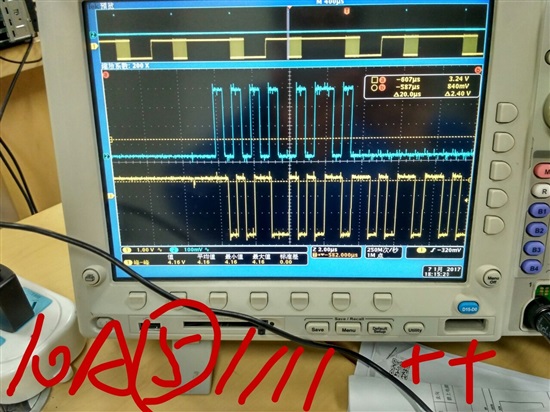

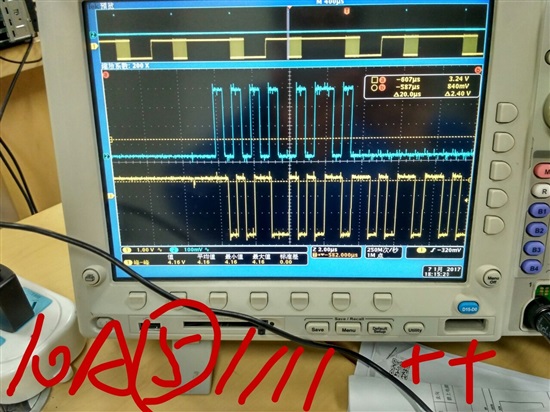

示波器图形如下。图上对应上位机(蓝线)发送的36个字节,帧头是AA 5A,

dsp同步发送(黄线)的第一个字节数值比后面的每个字节的值要少1(因为S_data[j]++),

数组初始化成1、2…36 再递增,就发现对应AA的数据是s[35](应该是要上一帧就发完的)。

所以很奇怪,各位大大能看出是什么原因么??

mangui zhang:

没有看出什么问题 实在不行就用IO口模拟吧

我想请教下一个我在开发过程中遇到的问题:

关于用F28335McBSP模拟spi收发数据,配置mcbspB成SPI模式,从模式和上位机通信,每次接收和发送数据长度为8位。上位机那边发出36×8位的数据(头两个八位数据为帧头0XAA和指令0X5A),dsp返回一些计算后的数据,采用如下代码(简化逻辑后的)。

for(j=0;j<36;j++) //Initialize data { S_data[j]=0; } while(1) //keep running:send data { for(m=0;m<36;m++)

{

McbspbRegs.DXR1.all = S_data[m];

while(McbspbRegs.SPCR1.bit.RRDY == 0 ) { } flagdate = McbspbRegs.DRR1.all; }

for(j=0;j<36;j++) //change send data { S_data[j]++; } }

但是根据示波器的结果观察看,dsp发出的数据不对,对应输入的36个数据,dsp发出的为:

S_data[35] S_data[0] S_data[1] S_data[2]…S_data[34]然后接收下一组36个数据,发出的还是这个顺序。

能够知道的是,S_data[35] 为上一周期数据的最后一个8位,不知道为什么会有延迟。

我这样的代码,逻辑上有问题吗,还是说寄存器的配置问题,我是设置的8位数据发送,36个字,对应寄存器设置如下:

void InitMcbspb(void)

{

// reset McBSP and SRG

McbspbRegs.SPCR2.bit.FRST=0;

McbspbRegs.SPCR2.bit.GRST=0;

McbspbRegs.SPCR2.bit.XRST=0;

McbspbRegs.SPCR1.bit.RRST=0;

// SPI mode

McbspbRegs.SPCR1.bit.DLB = 0;

McbspbRegs.SPCR1.bit.CLKSTP = 2;

// clock set as slave mode

McbspbRegs.PCR.bit.SCLKME = 0;

McbspbRegs.SRGR2.bit.CLKSM = 1;

// McbspbRegs.PCR.bit.CLKRM = 1;

McbspbRegs.PCR.bit.CLKXM = 0;

McbspbRegs.PCR.bit.CLKRP = 0; //jdp

McbspbRegs.PCR.bit.CLKXP = 0;

McbspbRegs.SRGR1.bit.CLKGDV = 1;

// FSG set as slave mode

//McbspbRegs.PCR.bit.FSRM = 0; //jdp

McbspbRegs.PCR.bit.FSXM = 0;

//McbspbRegs.PCR.bit.FSRP = 1; //jdp

McbspbRegs.PCR.bit.FSXP = 1;

//McbspbRegs.RCR2.bit.RDATDLY= 0;

//McbspbRegs.XCR2.bit.XDATDLY= 0;

// enable McBSP

delay_loop();

McbspbRegs.SPCR2.bit.GRST = 1;

clkg_delay_loop();

McbspbRegs.SPCR2.bit.XRST = 1;

McbspbRegs.SPCR1.bit.RRST = 1;

McbspbRegs.SPCR2.bit.FRST = 1;

}

void InitMcbspb8bit(void)

{

McbspbRegs.RCR1.bit.RFRLEN1=35; // 36-word

McbspbRegs.RCR1.bit.RWDLEN1=0; // 8-bit

McbspbRegs.XCR1.bit.XFRLEN1=35; // 8 word

McbspbRegs.XCR1.bit.XWDLEN1=0; // 8-bit

}

调了很久了,不论怎么设置寄存器和更改代码逻辑,都会有1~3个数据(每个数据8位)的延迟。

各位能帮我看看是哪里存在的问题吗?多谢了哈~

ps:

示波器图形如下。图上对应上位机(蓝线)发送的36个字节,帧头是AA 5A,

dsp同步发送(黄线)的第一个字节数值比后面的每个字节的值要少1(因为S_data[j]++),

数组初始化成1、2…36 再递增,就发现对应AA的数据是s[35](应该是要上一帧就发完的)。

所以很奇怪,各位大大能看出是什么原因么??

rookiecalf:

回复 mangui zhang:

建议做帧间延时处理,接收时,根据帧间的延时来做帧起始判断

我想请教下一个我在开发过程中遇到的问题:

关于用F28335McBSP模拟spi收发数据,配置mcbspB成SPI模式,从模式和上位机通信,每次接收和发送数据长度为8位。上位机那边发出36×8位的数据(头两个八位数据为帧头0XAA和指令0X5A),dsp返回一些计算后的数据,采用如下代码(简化逻辑后的)。

for(j=0;j<36;j++) //Initialize data { S_data[j]=0; } while(1) //keep running:send data { for(m=0;m<36;m++)

{

McbspbRegs.DXR1.all = S_data[m];

while(McbspbRegs.SPCR1.bit.RRDY == 0 ) { } flagdate = McbspbRegs.DRR1.all; }

for(j=0;j<36;j++) //change send data { S_data[j]++; } }

但是根据示波器的结果观察看,dsp发出的数据不对,对应输入的36个数据,dsp发出的为:

S_data[35] S_data[0] S_data[1] S_data[2]…S_data[34]然后接收下一组36个数据,发出的还是这个顺序。

能够知道的是,S_data[35] 为上一周期数据的最后一个8位,不知道为什么会有延迟。

我这样的代码,逻辑上有问题吗,还是说寄存器的配置问题,我是设置的8位数据发送,36个字,对应寄存器设置如下:

void InitMcbspb(void)

{

// reset McBSP and SRG

McbspbRegs.SPCR2.bit.FRST=0;

McbspbRegs.SPCR2.bit.GRST=0;

McbspbRegs.SPCR2.bit.XRST=0;

McbspbRegs.SPCR1.bit.RRST=0;

// SPI mode

McbspbRegs.SPCR1.bit.DLB = 0;

McbspbRegs.SPCR1.bit.CLKSTP = 2;

// clock set as slave mode

McbspbRegs.PCR.bit.SCLKME = 0;

McbspbRegs.SRGR2.bit.CLKSM = 1;

// McbspbRegs.PCR.bit.CLKRM = 1;

McbspbRegs.PCR.bit.CLKXM = 0;

McbspbRegs.PCR.bit.CLKRP = 0; //jdp

McbspbRegs.PCR.bit.CLKXP = 0;

McbspbRegs.SRGR1.bit.CLKGDV = 1;

// FSG set as slave mode

//McbspbRegs.PCR.bit.FSRM = 0; //jdp

McbspbRegs.PCR.bit.FSXM = 0;

//McbspbRegs.PCR.bit.FSRP = 1; //jdp

McbspbRegs.PCR.bit.FSXP = 1;

//McbspbRegs.RCR2.bit.RDATDLY= 0;

//McbspbRegs.XCR2.bit.XDATDLY= 0;

// enable McBSP

delay_loop();

McbspbRegs.SPCR2.bit.GRST = 1;

clkg_delay_loop();

McbspbRegs.SPCR2.bit.XRST = 1;

McbspbRegs.SPCR1.bit.RRST = 1;

McbspbRegs.SPCR2.bit.FRST = 1;

}

void InitMcbspb8bit(void)

{

McbspbRegs.RCR1.bit.RFRLEN1=35; // 36-word

McbspbRegs.RCR1.bit.RWDLEN1=0; // 8-bit

McbspbRegs.XCR1.bit.XFRLEN1=35; // 8 word

McbspbRegs.XCR1.bit.XWDLEN1=0; // 8-bit

}

调了很久了,不论怎么设置寄存器和更改代码逻辑,都会有1~3个数据(每个数据8位)的延迟。

各位能帮我看看是哪里存在的问题吗?多谢了哈~

ps:

示波器图形如下。图上对应上位机(蓝线)发送的36个字节,帧头是AA 5A,

dsp同步发送(黄线)的第一个字节数值比后面的每个字节的值要少1(因为S_data[j]++),

数组初始化成1、2…36 再递增,就发现对应AA的数据是s[35](应该是要上一帧就发完的)。

所以很奇怪,各位大大能看出是什么原因么??

HG:

上波形吧,看的清楚点

我想请教下一个我在开发过程中遇到的问题:

关于用F28335McBSP模拟spi收发数据,配置mcbspB成SPI模式,从模式和上位机通信,每次接收和发送数据长度为8位。上位机那边发出36×8位的数据(头两个八位数据为帧头0XAA和指令0X5A),dsp返回一些计算后的数据,采用如下代码(简化逻辑后的)。

for(j=0;j<36;j++) //Initialize data { S_data[j]=0; } while(1) //keep running:send data { for(m=0;m<36;m++)

{

McbspbRegs.DXR1.all = S_data[m];

while(McbspbRegs.SPCR1.bit.RRDY == 0 ) { } flagdate = McbspbRegs.DRR1.all; }

for(j=0;j<36;j++) //change send data { S_data[j]++; } }

但是根据示波器的结果观察看,dsp发出的数据不对,对应输入的36个数据,dsp发出的为:

S_data[35] S_data[0] S_data[1] S_data[2]…S_data[34]然后接收下一组36个数据,发出的还是这个顺序。

能够知道的是,S_data[35] 为上一周期数据的最后一个8位,不知道为什么会有延迟。

我这样的代码,逻辑上有问题吗,还是说寄存器的配置问题,我是设置的8位数据发送,36个字,对应寄存器设置如下:

void InitMcbspb(void)

{

// reset McBSP and SRG

McbspbRegs.SPCR2.bit.FRST=0;

McbspbRegs.SPCR2.bit.GRST=0;

McbspbRegs.SPCR2.bit.XRST=0;

McbspbRegs.SPCR1.bit.RRST=0;

// SPI mode

McbspbRegs.SPCR1.bit.DLB = 0;

McbspbRegs.SPCR1.bit.CLKSTP = 2;

// clock set as slave mode

McbspbRegs.PCR.bit.SCLKME = 0;

McbspbRegs.SRGR2.bit.CLKSM = 1;

// McbspbRegs.PCR.bit.CLKRM = 1;

McbspbRegs.PCR.bit.CLKXM = 0;

McbspbRegs.PCR.bit.CLKRP = 0; //jdp

McbspbRegs.PCR.bit.CLKXP = 0;

McbspbRegs.SRGR1.bit.CLKGDV = 1;

// FSG set as slave mode

//McbspbRegs.PCR.bit.FSRM = 0; //jdp

McbspbRegs.PCR.bit.FSXM = 0;

//McbspbRegs.PCR.bit.FSRP = 1; //jdp

McbspbRegs.PCR.bit.FSXP = 1;

//McbspbRegs.RCR2.bit.RDATDLY= 0;

//McbspbRegs.XCR2.bit.XDATDLY= 0;

// enable McBSP

delay_loop();

McbspbRegs.SPCR2.bit.GRST = 1;

clkg_delay_loop();

McbspbRegs.SPCR2.bit.XRST = 1;

McbspbRegs.SPCR1.bit.RRST = 1;

McbspbRegs.SPCR2.bit.FRST = 1;

}

void InitMcbspb8bit(void)

{

McbspbRegs.RCR1.bit.RFRLEN1=35; // 36-word

McbspbRegs.RCR1.bit.RWDLEN1=0; // 8-bit

McbspbRegs.XCR1.bit.XFRLEN1=35; // 8 word

McbspbRegs.XCR1.bit.XWDLEN1=0; // 8-bit

}

调了很久了,不论怎么设置寄存器和更改代码逻辑,都会有1~3个数据(每个数据8位)的延迟。

各位能帮我看看是哪里存在的问题吗?多谢了哈~

ps:

示波器图形如下。图上对应上位机(蓝线)发送的36个字节,帧头是AA 5A,

dsp同步发送(黄线)的第一个字节数值比后面的每个字节的值要少1(因为S_data[j]++),

数组初始化成1、2…36 再递增,就发现对应AA的数据是s[35](应该是要上一帧就发完的)。

所以很奇怪,各位大大能看出是什么原因么??

jianteng huang:

回复 HG:

我更新了帖子,上传了波形图,请帮忙看下~

我想请教下一个我在开发过程中遇到的问题:

关于用F28335McBSP模拟spi收发数据,配置mcbspB成SPI模式,从模式和上位机通信,每次接收和发送数据长度为8位。上位机那边发出36×8位的数据(头两个八位数据为帧头0XAA和指令0X5A),dsp返回一些计算后的数据,采用如下代码(简化逻辑后的)。

for(j=0;j<36;j++) //Initialize data { S_data[j]=0; } while(1) //keep running:send data { for(m=0;m<36;m++)

{

McbspbRegs.DXR1.all = S_data[m];

while(McbspbRegs.SPCR1.bit.RRDY == 0 ) { } flagdate = McbspbRegs.DRR1.all; }

for(j=0;j<36;j++) //change send data { S_data[j]++; } }

但是根据示波器的结果观察看,dsp发出的数据不对,对应输入的36个数据,dsp发出的为:

S_data[35] S_data[0] S_data[1] S_data[2]…S_data[34]然后接收下一组36个数据,发出的还是这个顺序。

能够知道的是,S_data[35] 为上一周期数据的最后一个8位,不知道为什么会有延迟。

我这样的代码,逻辑上有问题吗,还是说寄存器的配置问题,我是设置的8位数据发送,36个字,对应寄存器设置如下:

void InitMcbspb(void)

{

// reset McBSP and SRG

McbspbRegs.SPCR2.bit.FRST=0;

McbspbRegs.SPCR2.bit.GRST=0;

McbspbRegs.SPCR2.bit.XRST=0;

McbspbRegs.SPCR1.bit.RRST=0;

// SPI mode

McbspbRegs.SPCR1.bit.DLB = 0;

McbspbRegs.SPCR1.bit.CLKSTP = 2;

// clock set as slave mode

McbspbRegs.PCR.bit.SCLKME = 0;

McbspbRegs.SRGR2.bit.CLKSM = 1;

// McbspbRegs.PCR.bit.CLKRM = 1;

McbspbRegs.PCR.bit.CLKXM = 0;

McbspbRegs.PCR.bit.CLKRP = 0; //jdp

McbspbRegs.PCR.bit.CLKXP = 0;

McbspbRegs.SRGR1.bit.CLKGDV = 1;

// FSG set as slave mode

//McbspbRegs.PCR.bit.FSRM = 0; //jdp

McbspbRegs.PCR.bit.FSXM = 0;

//McbspbRegs.PCR.bit.FSRP = 1; //jdp

McbspbRegs.PCR.bit.FSXP = 1;

//McbspbRegs.RCR2.bit.RDATDLY= 0;

//McbspbRegs.XCR2.bit.XDATDLY= 0;

// enable McBSP

delay_loop();

McbspbRegs.SPCR2.bit.GRST = 1;

clkg_delay_loop();

McbspbRegs.SPCR2.bit.XRST = 1;

McbspbRegs.SPCR1.bit.RRST = 1;

McbspbRegs.SPCR2.bit.FRST = 1;

}

void InitMcbspb8bit(void)

{

McbspbRegs.RCR1.bit.RFRLEN1=35; // 36-word

McbspbRegs.RCR1.bit.RWDLEN1=0; // 8-bit

McbspbRegs.XCR1.bit.XFRLEN1=35; // 8 word

McbspbRegs.XCR1.bit.XWDLEN1=0; // 8-bit

}

调了很久了,不论怎么设置寄存器和更改代码逻辑,都会有1~3个数据(每个数据8位)的延迟。

各位能帮我看看是哪里存在的问题吗?多谢了哈~

ps:

示波器图形如下。图上对应上位机(蓝线)发送的36个字节,帧头是AA 5A,

dsp同步发送(黄线)的第一个字节数值比后面的每个字节的值要少1(因为S_data[j]++),

数组初始化成1、2…36 再递增,就发现对应AA的数据是s[35](应该是要上一帧就发完的)。

所以很奇怪,各位大大能看出是什么原因么??

jianteng huang:

回复 rookiecalf:

Changjiang Liu

建议做帧间延时处理,接收�,根据帧间的延时来做帧起始判断

我想请教下一个我在开发过程中遇到的问题:

关于用F28335McBSP模拟spi收发数据,配置mcbspB成SPI模式,从模式和上位机通信,每次接收和发送数据长度为8位。上位机那边发出36×8位的数据(头两个八位数据为帧头0XAA和指令0X5A),dsp返回一些计算后的数据,采用如下代码(简化逻辑后的)。

for(j=0;j<36;j++) //Initialize data { S_data[j]=0; } while(1) //keep running:send data { for(m=0;m<36;m++)

{

McbspbRegs.DXR1.all = S_data[m];

while(McbspbRegs.SPCR1.bit.RRDY == 0 ) { } flagdate = McbspbRegs.DRR1.all; }

for(j=0;j<36;j++) //change send data { S_data[j]++; } }

但是根据示波器的结果观察看,dsp发出的数据不对,对应输入的36个数据,dsp发出的为:

S_data[35] S_data[0] S_data[1] S_data[2]…S_data[34]然后接收下一组36个数据,发出的还是这个顺序。

能够知道的是,S_data[35] 为上一周期数据的最后一个8位,不知道为什么会有延迟。

我这样的代码,逻辑上有问题吗,还是说寄存器的配置问题,我是设置的8位数据发送,36个字,对应寄存器设置如下:

void InitMcbspb(void)

{

// reset McBSP and SRG

McbspbRegs.SPCR2.bit.FRST=0;

McbspbRegs.SPCR2.bit.GRST=0;

McbspbRegs.SPCR2.bit.XRST=0;

McbspbRegs.SPCR1.bit.RRST=0;

// SPI mode

McbspbRegs.SPCR1.bit.DLB = 0;

McbspbRegs.SPCR1.bit.CLKSTP = 2;

// clock set as slave mode

McbspbRegs.PCR.bit.SCLKME = 0;

McbspbRegs.SRGR2.bit.CLKSM = 1;

// McbspbRegs.PCR.bit.CLKRM = 1;

McbspbRegs.PCR.bit.CLKXM = 0;

McbspbRegs.PCR.bit.CLKRP = 0; //jdp

McbspbRegs.PCR.bit.CLKXP = 0;

McbspbRegs.SRGR1.bit.CLKGDV = 1;

// FSG set as slave mode

//McbspbRegs.PCR.bit.FSRM = 0; //jdp

McbspbRegs.PCR.bit.FSXM = 0;

//McbspbRegs.PCR.bit.FSRP = 1; //jdp

McbspbRegs.PCR.bit.FSXP = 1;

//McbspbRegs.RCR2.bit.RDATDLY= 0;

//McbspbRegs.XCR2.bit.XDATDLY= 0;

// enable McBSP

delay_loop();

McbspbRegs.SPCR2.bit.GRST = 1;

clkg_delay_loop();

McbspbRegs.SPCR2.bit.XRST = 1;

McbspbRegs.SPCR1.bit.RRST = 1;

McbspbRegs.SPCR2.bit.FRST = 1;

}

void InitMcbspb8bit(void)

{

McbspbRegs.RCR1.bit.RFRLEN1=35; // 36-word

McbspbRegs.RCR1.bit.RWDLEN1=0; // 8-bit

McbspbRegs.XCR1.bit.XFRLEN1=35; // 8 word

McbspbRegs.XCR1.bit.XWDLEN1=0; // 8-bit

}

调了很久了,不论怎么设置寄存器和更改代码逻辑,都会有1~3个数据(每个数据8位)的延迟。

各位能帮我看看是哪里存在的问题吗?多谢了哈~

ps:

示波器图形如下。图上对应上位机(蓝线)发送的36个字节,帧头是AA 5A,

dsp同步发送(黄线)的第一个字节数值比后面的每个字节的值要少1(因为S_data[j]++),

数组初始化成1、2…36 再递增,就发现对应AA的数据是s[35](应该是要上一帧就发完的)。

所以很奇怪,各位大大能看出是什么原因么??

jianteng huang:

回复 HG:

HG

上波形吧,看的清楚点

TI中文支持网

TI中文支持网