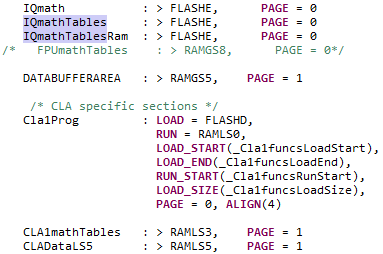

本人在TI例程cla_adc_fir32_cpu01中添加TIMER0中断,增加中断处理的内容,在各个中断进入时拉高相应的管脚电平,在各自处理完内容后又都拉低相应的管脚电平,在测试中发现两个中断相互产生了影响,并不是像手册所说的CLA协处理器的独立性,不知道哪里出了问题,请高手指教.

Shine:

请问用的是哪款芯片?

kafei zhang:

回复 Shine:

TMS320F28377S,后续再准备用TMS320F28377D

Shine:

回复 kafei zhang:

有专门的论坛咨询。

C2000™ 32位实时 MCU

TI中文支持网

TI中文支持网