代码如下

EPwm3Regs.TBPRD =60000000/(2*fz); // Period = 1600 TBCLK counts

EPwm3Regs.TBPHS.half.TBPHS = 0; // Set Phase register to zero

EPwm3Regs.TBCTR = 0x0000;

EPwm3Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm3Regs.TBCTL.bit.CLKDIV = TB_DIV1;// Clear counter

EPwm3Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Symmetrical mode

EPwm3Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Slave module

EPwm3Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm3Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // sync flow-through

EPwm3Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm3Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm3Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // load on CTR=Zero

EPwm3Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // load on CTR=Zero

EPwm3Regs.AQCTLA.bit.CAU = AQ_CLEAR; // set actions for EPWM2A

EPwm3Regs.AQCTLA.bit.CAD = AQ_SET;

EPwm3Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable Dead-band module

EPwm3Regs.DBCTL.bit.POLSEL = DB_ACTV_LOC; // Active Hi complementary

EPwm3Regs.DBFED = 120; // FED = 50 TBCLKs

EPwm3Regs.DBRED = 120; // RED = 50 TBCLKs

EPwm1Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; // Select INT on Zero event

EPwm1Regs.ETSEL.bit.INTEN = 1; // Enable INT

EPwm1Regs.ETPS.bit.INTPRD = ET_1ST;

以上是三组PWM设置中的一组其他相同,其中载波为15K。

EALLOW;

AdcRegs.ADCCTL1.bit.INTPULSEPOS = 1; //ADCINT1 trips after AdcResults latch

AdcRegs.INTSEL1N2.bit.INT1E = 1; //Enabled ADCINT1

AdcRegs.INTSEL1N2.bit.INT1CONT = 0; //Disable ADCINT1 Continuous mode

AdcRegs.INTSEL1N2.bit.INT1SEL = 2; //setup EOC2 to trigger ADCINT1 to fire

AdcRegs.ADCSOC0CTL.bit.CHSEL = 1; //set SOC0 channel select to ADCINA4(dummy sample for rev0 errata workaround)

AdcRegs.ADCSOC1CTL.bit.CHSEL = 1; //set SOC1 channel select to ADCINA4

AdcRegs.ADCSOC2CTL.bit.CHSEL = 2; //set SOC2 channel select to ADCINA2

AdcRegs.ADCSOC0CTL.bit.TRIGSEL = 13; //set SOC0 start trigger on EPWM1A, due to round-robin SOC0 converts first then SOC1, then SOC2

AdcRegs.ADCSOC1CTL.bit.TRIGSEL = 13; //set SOC1 start trigger on EPWM1A, due to round-robin SOC0 converts first then SOC1, then SOC2

AdcRegs.ADCSOC2CTL.bit.TRIGSEL = 13; //set SOC2 start trigger on EPWM1A, due to round-robin SOC0 converts first then SOC1, then SOC2

AdcRegs.ADCSOC0CTL.bit.ACQPS = 6; //set SOC0 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

AdcRegs.ADCSOC1CTL.bit.ACQPS = 6; //set SOC1 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

AdcRegs.ADCSOC2CTL.bit.ACQPS = 6; //set SOC2 S/H Window to 7 ADC Clock Cycles, (6 ACQPS plus 1)

EDIS;

// Assumes ePWM1 clock is already enabled in InitSysCtrl();

EPwm5Regs.ETSEL.bit.SOCAEN = 1; // Enable SOC on A group

EPwm5Regs.ETSEL.bit.SOCASEL = 4; // Select SOC from from CPMA on upcount

EPwm5Regs.ETPS.bit.SOCAPRD = 1; // Generate pulse on 1st event

EPwm5Regs.CMPA.half.CMPA = 0x0080; // Set compare A value

EPwm5Regs.TBPRD = 0XFFFF; // Set period for ePWM1

EPwm5Regs.TBCTL.bit.CTRMODE = 0; // count up and start

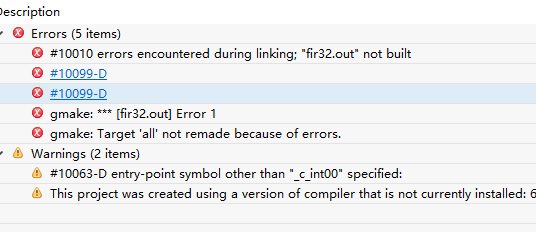

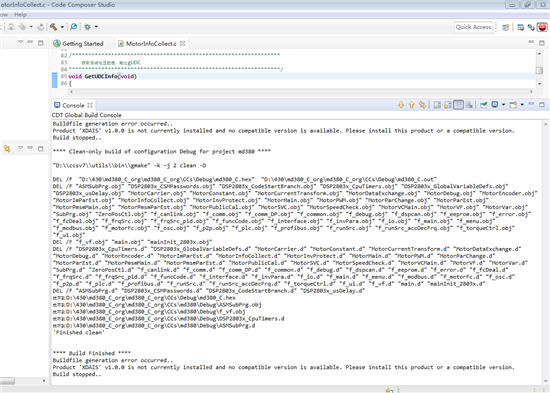

以上是ADC采样程序,但是实际上,PWM能输出,但是ADC不能进入中断,如果把EPWM的中断去掉,那么ADC采样就能用。请问这是什么原因?跪求。

TI中文支持网

TI中文支持网