all:

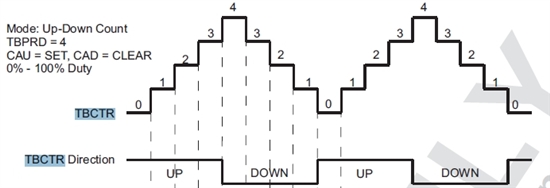

我在配置两路下降沿可控的PWM波形时,发现当配置UP-DOWN模式下,CBD在零点清零或者置位都无效,因为计数0是针对上升计数(UP)时的.

是否有人遇到同样问题??

配置如下:

EALLOW;

// Timer Base:

Regs->TBCTL.bit.HSPCLKDIV = 0; // Clock ratio to SYSCLKOUT

Regs->TBCTL.bit.CLKDIV = 0; // Slow just to observe on the scope

Regs->TBCTL.bit.CTRMODE = 2; // 0:up 1:down 2:updown mode

Regs->TBCTR = 0x0000; // Clear counter

Regs->CMPA.bit.CMPA = 0;

Regs->CMPB.bit.CMPB = 0;

// ———-PWM的同步,和相移 ——————-

// SYNCOSEL bit:

// 00 EPWMxSYNCI: 从模式接收同步信号

// 01 CTR = zero: Time-base counter equal to zero (TBCTR = 0x0000)

// 10 CTR = CMPB : (TBCTR = CMPB)时发出同步信号

Regs->TBCTL.bit.SYNCOSEL = master ? 1 : 0;

Regs->TBCTL.bit.PHSEN = master ? 0 : 1; // 0:master,1: slave

Regs->TBCTL.bit.PRDLD = 0; // 0: enable TBPRD shadow mode, load TBPRD @ TPCTR=0

Regs->CMPCTL.bit.SHDWAMODE = 0; // 0: enable CMPA shadow mode

Regs->CMPCTL.bit.SHDWBMODE = 0; // 0: enable CMPB shadow mode

Regs->CMPCTL.bit.LOADAMODE = 0; // 00 Load on CTR = Zero

Regs->CMPCTL.bit.LOADBMODE = 0; // 00 Load on CTR = Zero

Regs->DBCTL.bit.IN_MODE = 2; // EPWMxA In (from the action-qualifier) is the source for

// both falling-edge and rising-edge delay.

Regs->DBCTL.bit.POLSEL = 3; // Active high complementary (AHC). EPWMxB is inverted.

Regs->DBCTL.bit.OUT_MODE = 3; // Dead-band is fully enabled for both rising-edge delay on output EPWMxA and falling-edge

// delay on output EPWMxB. The input signal for the delay is determined by DBCTL[IN_MODE].

Regs->AQCTLA.bit.ZRO =AQ_SET;

Regs->AQCTLA.bit.CAU = AQ_CLEAR;

Regs->AQCTLB.bit.PRD = AQ_SET;

Regs->AQCTLB.bit.CBD =AQ_CLEAR;

// 对于PWM和SR,以下部分是不同的:

Regs->DBRED.bit.DBRED = 0;

Regs->DBFED.bit.DBFED = 0;

#ifndef ENABLE_TZ

#error ENABLE_TZ not defined

#endif

#if !ENABLE_TZ

Regs->TZSEL.bit.OSHT1 = 1;

#endif

Regs->TZCTL.bit.TZA = 1; // TZA=1:force EPWMxA to high 2:force EPWMxA to low

Regs->TZCTL.bit.TZB = 1; // TZB=1:force EPWMxB to high 2:force EPWMxB to low

EDIS;

yiqun zheng:

顶一下~~

TI中文支持网

TI中文支持网