1.外部ADC要求输入的时钟信号高电平最小电压为3.5V,DSP引脚输出高电平为3.3V,我能不能用DSP直接驱动?如果不能我使用什么芯片来进行电压转换?

2.我要求外部ADC的时钟输入频率为5M(采样率为5M),由于读取ADC的转换数据(12位并行)需要外部接口XINTF模块,我本打算使用XINTF模块的XCLKOUT输出作为外部ADC的时钟信号,但是它的频率最小只能是SYSCLKOUT/4,我要求设置系统时钟为150M,所以满足不了5M时钟信号输出。

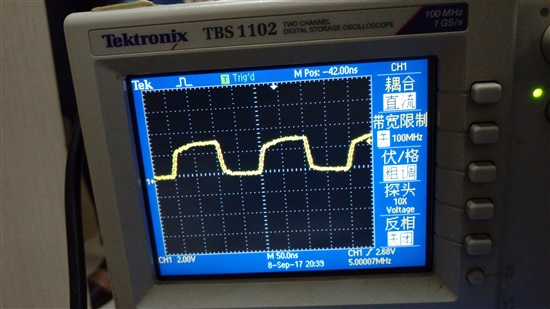

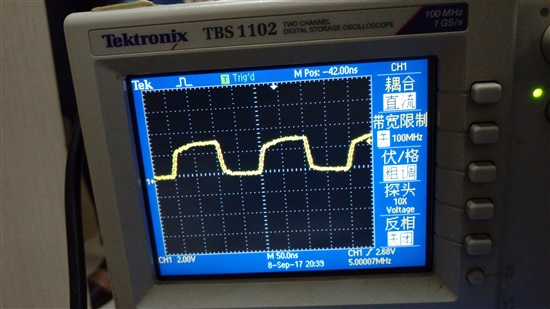

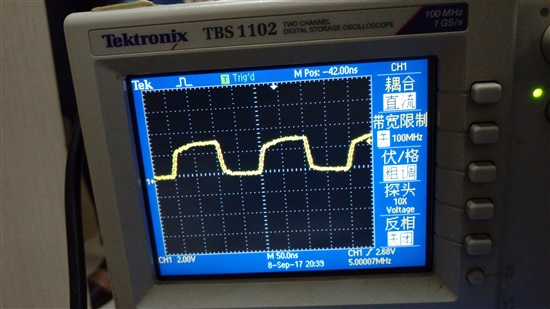

后来又用EPWM模块产生占空比为50%频率为5M的PWM,打算将其作为外部ADC时钟信号,但是经过测试输出的PWM波形很差,如下图(直观上看,考量时钟信号好坏的参数不太了解)。后来又打算使用HRPWM模块(高精度脉宽调制模块),但是我的理解是HRPWM只是对占空比能实现较高精度的调节,我们输出的是占空比50%的波形,所以并没有使用到扩展的高精度寄存器,用HRPWM和EPWM产生的占空比为50%频率为5M的PWM波形是一样的。我理解的对吗?

3.如果这几种方法输出的时钟信号都不能满足外部ADC对时钟信号的高度要求,那使用时钟芯片产生5M的时钟信号精度和波形是不是比以上好得多?有推荐的时钟芯片吗?

Zhibin Yang:

TI工程师们和各位大神们

1.外部ADC要求输入的时钟信号高电平最小电压为3.5V,DSP引脚输出高电平为3.3V,我能不能用DSP直接驱动?如果不能我使用什么芯片来进行电压转换?

2.我要求外部ADC的时钟输入频率为5M(采样率为5M),由于读取ADC的转换数据(12位并行)需要外部接口XINTF模块,我本打算使用XINTF模块的XCLKOUT输出作为外部ADC的时钟信号,但是它的频率最小只能是SYSCLKOUT/4,我要求设置系统时钟为150M,所以满足不了5M时钟信号输出。

后来又用EPWM模块产生占空比为50%频率为5M的PWM,打算将其作为外部ADC时钟信号,但是经过测试输出的PWM波形很差,如下图(直观上看,考量时钟信号好坏的参数不太了解)。后来又打算使用HRPWM模块(高精度脉宽调制模块),但是我的理解是HRPWM只是对占空比能实现较高精度的调节,我们输出的是占空比50%的波形,所以并没有使用到扩展的高精度寄存器,用HRPWM和EPWM产生的占空比为50%频率为5M的PWM波形是一样的。我理解的对吗?

3.如果这几种方法输出的时钟信号都不能满足外部ADC对时钟信号的高度要求,那使用时钟芯片产生5M的时钟信号精度和波形是不是比以上好得多?有推荐的时钟芯片吗?

mangui zhang:

IO口肯定是不行 应该到不了这么快的翻转

clkout应该是可以到5M的 你通过调整SYSYCLK和分频关系

个人觉得幅度肯定是可以驱动ADC的 如果效果不好

建议将输出的CLK先隔直 然后加直流分量 让最高幅度能到需要幅度

1.外部ADC要求输入的时钟信号高电平最小电压为3.5V,DSP引脚输出高电平为3.3V,我能不能用DSP直接驱动?如果不能我使用什么芯片来进行电压转换?

2.我要求外部ADC的时钟输入频率为5M(采样率为5M),由于读取ADC的转换数据(12位并行)需要外部接口XINTF模块,我本打算使用XINTF模块的XCLKOUT输出作为外部ADC的时钟信号,但是它的频率最小只能是SYSCLKOUT/4,我要求设置系统时钟为150M,所以满足不了5M时钟信号输出。

后来又用EPWM模块产生占空比为50%频率为5M的PWM,打算将其作为外部ADC时钟信号,但是经过测试输出的PWM波形很差,如下图(直观上看,考量时钟信号好坏的参数不太了解)。后来又打算使用HRPWM模块(高精度脉宽调制模块),但是我的理解是HRPWM只是对占空比能实现较高精度的调节,我们输出的是占空比50%的波形,所以并没有使用到扩展的高精度寄存器,用HRPWM和EPWM产生的占空比为50%频率为5M的PWM波形是一样的。我理解的对吗?

3.如果这几种方法输出的时钟信号都不能满足外部ADC对时钟信号的高度要求,那使用时钟芯片产生5M的时钟信号精度和波形是不是比以上好得多?有推荐的时钟芯片吗?

Zhibin Yang:

回复 mangui zhang:

CLKOUT是可以到5M,但是我的SYSCLK设置是150M,不改变SYSCLK的情况下CLKOUT分频不能输出5M。

我还没试效果,效果肯定不会太好,您说的改变CLK幅值的方法肯定会引入噪声导致CLK效果更差,不如直接用时钟芯片。

TI中文支持网

TI中文支持网