大家好!有个项目用到了TI的TMS320C28346,但自己设计的给DSP供电的电源模块还有部分问题,现在想用直流电源直接给DSP供电;

供电方法如下:

先供电1.2V(核心电压),然后供电3.3V(外设电压),1.8V由电路板正常电压变换模块提供(3.3V降到1.8V),手动操作完成,核心

电压到外设电压延时估计得有数秒,但是DSP手册(Power Sequencing)有如下描述,需要在5ms以内上电,不知道以上操作会不会损坏

DSP或者合乎规范?

期望经验人士发表下看法!

song liu7:

DSP手册(Power Sequencing)有如下描述:

In any configuration, all the rails should ramp up within tpup (5 ms, typical) to allow early stability of clocks and IOs.

自己顶下

大家好!有个项目用到了TI的TMS320C28346,但自己设计的给DSP供电的电源模块还有部分问题,现在想用直流电源直接给DSP供电;

供电方法如下:

先供电1.2V(核心电压),然后供电3.3V(外设电压),1.8V由电路板正常电压变换模块提供(3.3V降到1.8V),手动操作完成,核心

电压到外设电压延时估计得有数秒,但是DSP手册(Power Sequencing)有如下描述,需要在5ms以内上电,不知道以上操作会不会损坏

DSP或者合乎规范?

期望经验人士发表下看法!

Seven Han:

手动操作完成,核心电压到外设电压延时估计得有数秒,

数据手册的6.9 Power Sequencing对上电顺序及其原因有说明,是为了保证芯片正常复位。

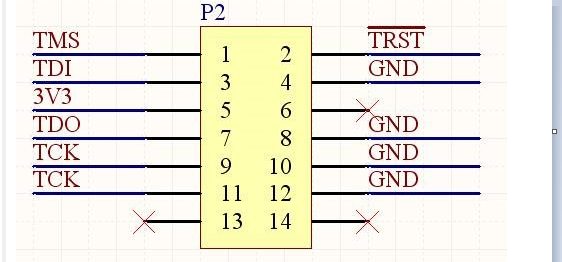

手动操作不知是否有保证两个电压上电间隔以确保不会烧坏芯片。有参考设计:controlCARDs\CC2834xHWdevPkg

No special requirements are placed on the power up/down sequence of the various power pins to ensurethe correct reset state for all the modules. However, if the 3.3-V transistors in the level shifting outputbuffers of the I/O pins are powered prior to the 1.1-V/1.2-V transistors, it is possible for the output buffersto turn on, causing a glitch to occur on the pin during power up. To avoid this behavior, power theVDD pins prior to or simultaneously with the VDDIO pins, ensuring that the VDD pins have reached 0.7-Vbefore the VDDIO pins reach 0.7 V. The 1.8-V rail for the PLL and oscillator logic can be powered up alongwith VDD/VDDIO rails. The 1.8-V rail must be powered even if the PLL is not used. It should never be leftunpowered. In any configuration, all the rails should ramp up within tpup (5 ms, typical) to allow earlystability of clocks and IOs.

大家好!有个项目用到了TI的TMS320C28346,但自己设计的给DSP供电的电源模块还有部分问题,现在想用直流电源直接给DSP供电;

供电方法如下:

先供电1.2V(核心电压),然后供电3.3V(外设电压),1.8V由电路板正常电压变换模块提供(3.3V降到1.8V),手动操作完成,核心

电压到外设电压延时估计得有数秒,但是DSP手册(Power Sequencing)有如下描述,需要在5ms以内上电,不知道以上操作会不会损坏

DSP或者合乎规范?

期望经验人士发表下看法!

song liu7:

回复 Seven Han:

谢谢,不知道其他人有没操作经验

大家好!有个项目用到了TI的TMS320C28346,但自己设计的给DSP供电的电源模块还有部分问题,现在想用直流电源直接给DSP供电;

供电方法如下:

先供电1.2V(核心电压),然后供电3.3V(外设电压),1.8V由电路板正常电压变换模块提供(3.3V降到1.8V),手动操作完成,核心

电压到外设电压延时估计得有数秒,但是DSP手册(Power Sequencing)有如下描述,需要在5ms以内上电,不知道以上操作会不会损坏

DSP或者合乎规范?

期望经验人士发表下看法!

mangui zhang:

上电顺序会导致的问题:

1.上电瞬间功耗增大

2.导致加载不能完成,启动失败

但不至于损坏,我建议你全部一起上,别手动控制上电顺序

大家好!有个项目用到了TI的TMS320C28346,但自己设计的给DSP供电的电源模块还有部分问题,现在想用直流电源直接给DSP供电;

供电方法如下:

先供电1.2V(核心电压),然后供电3.3V(外设电压),1.8V由电路板正常电压变换模块提供(3.3V降到1.8V),手动操作完成,核心

电压到外设电压延时估计得有数秒,但是DSP手册(Power Sequencing)有如下描述,需要在5ms以内上电,不知道以上操作会不会损坏

DSP或者合乎规范?

期望经验人士发表下看法!

mangui zhang:

上电顺序会导致的问题:

1.上电瞬间功耗增大

2.导致加载不能完成,启动失败

但不至于损坏,我建议你全部一起上,别手动控制上电顺序

大家好!有个项目用到了TI的TMS320C28346,但自己设计的给DSP供电的电源模块还有部分问题,现在想用直流电源直接给DSP供电;

供电方法如下:

先供电1.2V(核心电压),然后供电3.3V(外设电压),1.8V由电路板正常电压变换模块提供(3.3V降到1.8V),手动操作完成,核心

电压到外设电压延时估计得有数秒,但是DSP手册(Power Sequencing)有如下描述,需要在5ms以内上电,不知道以上操作会不会损坏

DSP或者合乎规范?

期望经验人士发表下看法!

song liu7:

回复 mangui zhang:

@mangui zhang,好的,谢谢

大家好!有个项目用到了TI的TMS320C28346,但自己设计的给DSP供电的电源模块还有部分问题,现在想用直流电源直接给DSP供电;

供电方法如下:

先供电1.2V(核心电压),然后供电3.3V(外设电压),1.8V由电路板正常电压变换模块提供(3.3V降到1.8V),手动操作完成,核心

电压到外设电压延时估计得有数秒,但是DSP手册(Power Sequencing)有如下描述,需要在5ms以内上电,不知道以上操作会不会损坏

DSP或者合乎规范?

期望经验人士发表下看法!

song liu7:

回复 mangui zhang:

@mangui zhang,不过手册上的上电时序有如下描述:

To avoid this behavior, power the VDD pins prior to or simultaneously with the VDDIO pins, ensuring that the VDD pins have reached 0.7-Vbefore the VDDIO pins reach 0.7 V.

即核心电压1.2V优先于3.3V上电

TI中文支持网

TI中文支持网