1.28062的fifo发送中断触发级别如果设置为4的时候一直进入中断,请问如果想每次发送四个16位数据再进入中断是不是需要将发送触发级别设置为0?即

SpibRegs.SPIFFTX.all=0xC020; // Enable FIFO's, set TX FIFO level to 4

SpibRegs.SPIFFRX.all=0x0024; // Set RX FIFO level to 4

2.级别如果设置为0,空闲状态如何避免一直进入发送中断此时却没有数据需要发送?

Emma Wang:

不太清楚你的Fifo的中断是如何编写的,不过发送4个16bit数据后再进中断触发级别是应该设置为4的。

也就是SPIFFTX的后五位设置为几,就能够一次发送几个word后再中断。2806X系列芯片最大支持4-level FIFO

你可以参考TI的官方代码:

C:\ti\controlSUITE\device_support\f2806x\v151\F2806x_examples_ccsv5\spi_loopback_interrupts

一般不会设置中断级别为0。

1.28062的fifo发送中断触发级别如果设置为4的时候一直进入中断,请问如果想每次发送四个16位数据再进入中断是不是需要将发送触发级别设置为0?即

SpibRegs.SPIFFTX.all=0xC020; // Enable FIFO's, set TX FIFO level to 4

SpibRegs.SPIFFRX.all=0x0024; // Set RX FIFO level to 4

2.级别如果设置为0,空闲状态如何避免一直进入发送中断此时却没有数据需要发送?

ming zheng8:

回复 Emma Wang:

我现在也是按这个例程改的,28062的spi fifo深度最大只有4级,如果我想发送数据时4级填满再发,中断触发级别是设置为0,但为什么你说一般不会设置中断级别为0呢?还有,往发送buf里填充数据能否在接收中断中处理?

1.28062的fifo发送中断触发级别如果设置为4的时候一直进入中断,请问如果想每次发送四个16位数据再进入中断是不是需要将发送触发级别设置为0?即

SpibRegs.SPIFFTX.all=0xC020; // Enable FIFO's, set TX FIFO level to 4

SpibRegs.SPIFFRX.all=0x0024; // Set RX FIFO level to 4

2.级别如果设置为0,空闲状态如何避免一直进入发送中断此时却没有数据需要发送?

Emma Wang:

回复 ming zheng8:

建议你将这两个寄存器设置为:

SpibRegs.SPIFFTX.all=0xC024 // Enable FIFO's, set TX FIFO level to 4SpibRegs.SPIFFRX.all=0x0024; // Set RX FIFO level to 4

同时观察发送数组sdata和接收数组rdata的情况,

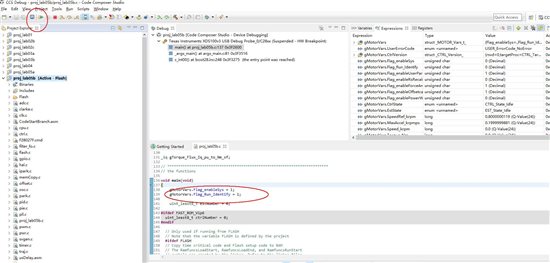

我在接收中断中设置了断点,观察到的数据情况如下:

发送sdata的数字刚刚好比接收rdata的数字多1,与预期相符。

1.28062的fifo发送中断触发级别如果设置为4的时候一直进入中断,请问如果想每次发送四个16位数据再进入中断是不是需要将发送触发级别设置为0?即

SpibRegs.SPIFFTX.all=0xC020; // Enable FIFO's, set TX FIFO level to 4

SpibRegs.SPIFFRX.all=0x0024; // Set RX FIFO level to 4

2.级别如果设置为0,空闲状态如何避免一直进入发送中断此时却没有数据需要发送?

ming zheng8:

回复 Emma Wang:

我把发送中断级别设置为4时,会一直进入中断(此时发送fifo里的字数永远小于等于4),影响其他进程,导致控制板上的键盘一直处于通讯故障(键盘采用sci中断通讯)。所以才将中断级别设置为0。

还有一个问题让我纠结,

发送中断时(或者接收中断中处理填充发送fifo时),填充发送fifo的buf需要时间,比如1微秒,1M的波特率时这个1微秒没发送数据,错过了1个时钟,然后再发送的数据能发完整吗?

期待回复..

TI中文支持网

TI中文支持网