大家好,我们测试了很多块板子,但有一块板子上主从DSP(F28335)的复位引脚有问题。

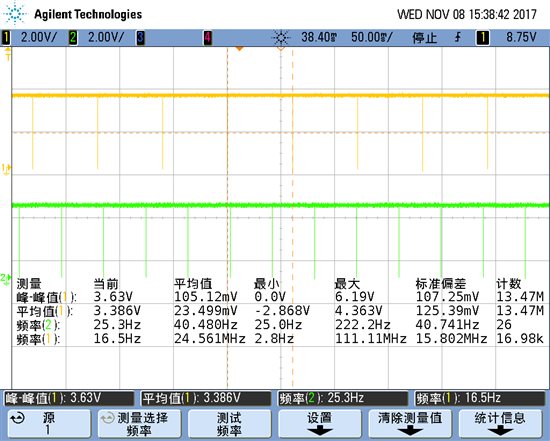

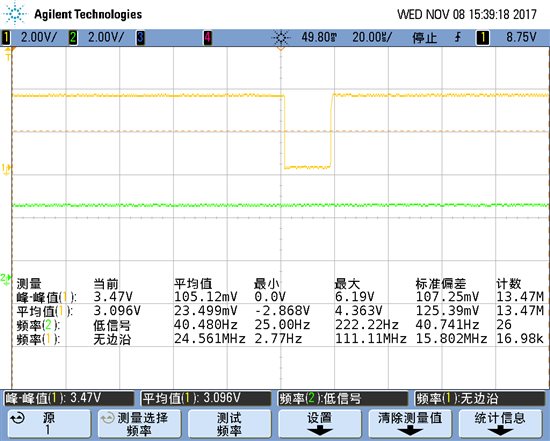

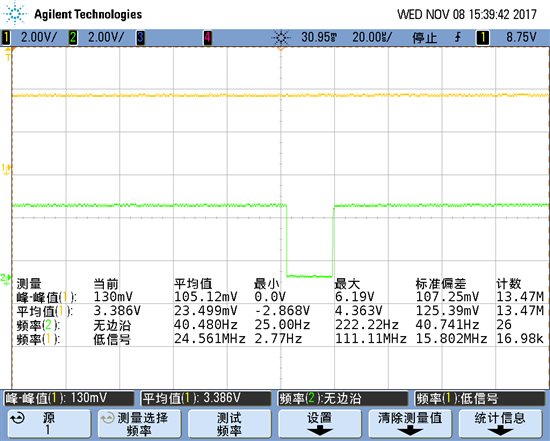

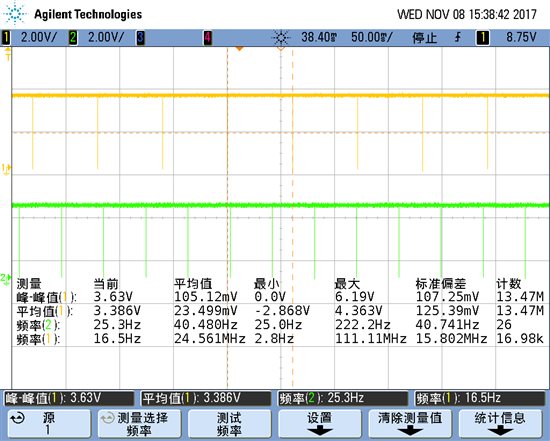

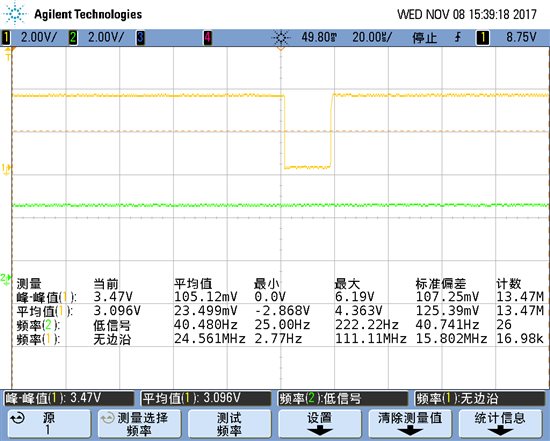

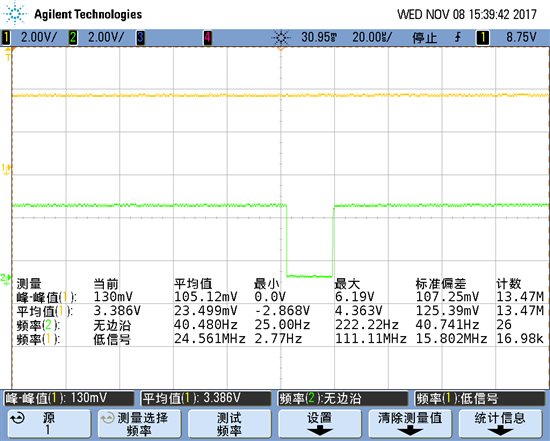

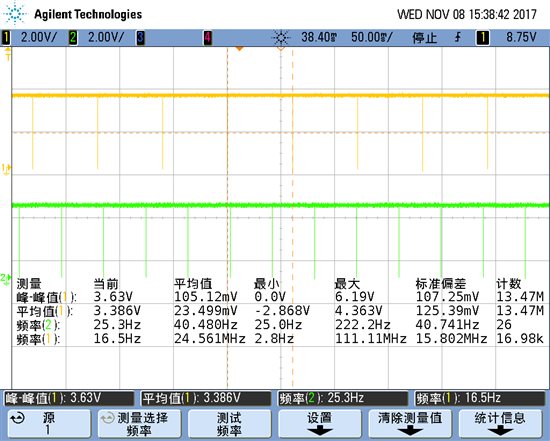

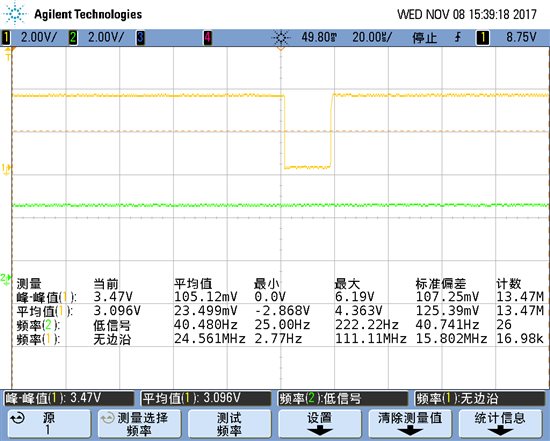

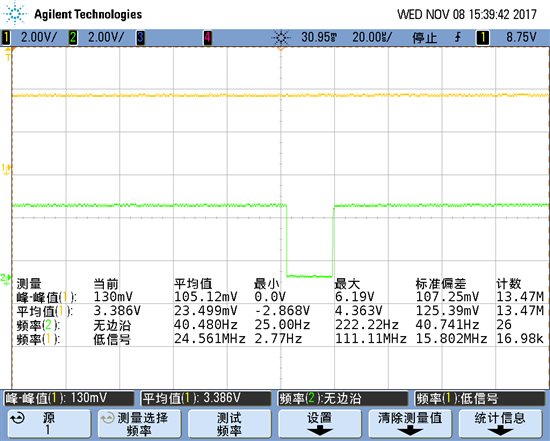

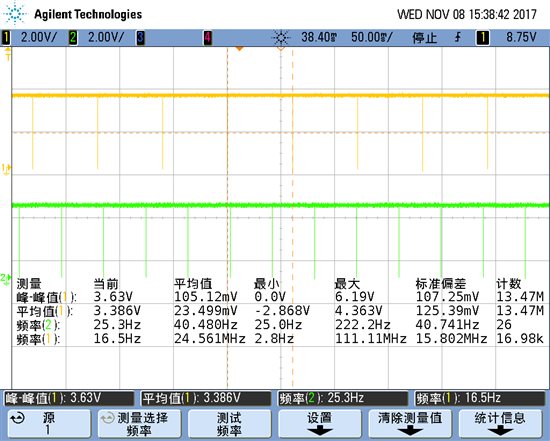

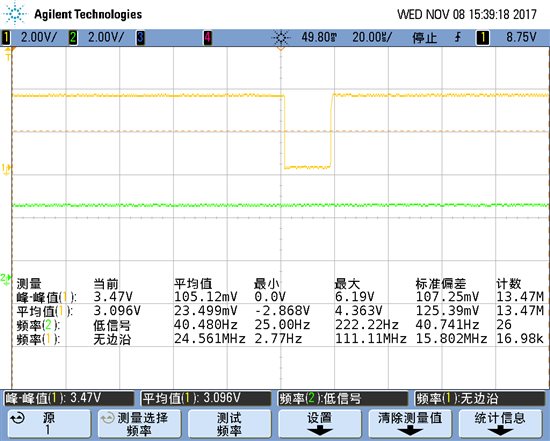

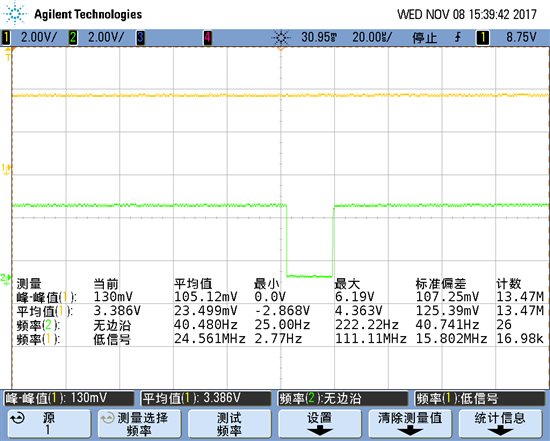

所设计的板子有主从DSP,两者的复位引脚应该在经过一段时间后到高电平,这样DSP才能正常启动。现两块DSP的测试程序都已经烧入,但如下图所示,两块DSP复位引脚XRS引脚上电后,其有周期性的低信号,导致两者一直处于复位状态,而无法正常启动。主从DSP上低电平的周期不同,但低电平的脉冲宽度都约为20us。

现在对比之前正常的板子,均无此现象,因此我们十分不解,希望大神们能答疑解惑,谢谢啦!

Seven Han:

看门狗默认是开启的,您的测试程序是否有关闭。

参考下这边帖子:http://www.deyisupport.com/question_answer/microcontrollers/c2000/f/56/p/139942/393755.aspx

大家好,我们测试了很多块板子,但有一块板子上主从DSP(F28335)的复位引脚有问题。

所设计的板子有主从DSP,两者的复位引脚应该在经过一段时间后到高电平,这样DSP才能正常启动。现两块DSP的测试程序都已经烧入,但如下图所示,两块DSP复位引脚XRS引脚上电后,其有周期性的低信号,导致两者一直处于复位状态,而无法正常启动。主从DSP上低电平的周期不同,但低电平的脉冲宽度都约为20us。

现在对比之前正常的板子,均无此现象,因此我们十分不解,希望大神们能答疑解惑,谢谢啦!

mangui zhang:

检查boot引脚设置是否可靠 应该是在一直加载 加载没成功

大家好,我们测试了很多块板子,但有一块板子上主从DSP(F28335)的复位引脚有问题。

所设计的板子有主从DSP,两者的复位引脚应该在经过一段时间后到高电平,这样DSP才能正常启动。现两块DSP的测试程序都已经烧入,但如下图所示,两块DSP复位引脚XRS引脚上电后,其有周期性的低信号,导致两者一直处于复位状态,而无法正常启动。主从DSP上低电平的周期不同,但低电平的脉冲宽度都约为20us。

现在对比之前正常的板子,均无此现象,因此我们十分不解,希望大神们能答疑解惑,谢谢啦!

Lihui Liu1:

回复 Seven Han:

非常感谢,通过查找,我们发现应该是控制DSP的FPGA虚焊了,所以导致DSP在不断的复位~

大家好,我们测试了很多块板子,但有一块板子上主从DSP(F28335)的复位引脚有问题。

所设计的板子有主从DSP,两者的复位引脚应该在经过一段时间后到高电平,这样DSP才能正常启动。现两块DSP的测试程序都已经烧入,但如下图所示,两块DSP复位引脚XRS引脚上电后,其有周期性的低信号,导致两者一直处于复位状态,而无法正常启动。主从DSP上低电平的周期不同,但低电平的脉冲宽度都约为20us。

现在对比之前正常的板子,均无此现象,因此我们十分不解,希望大神们能答疑解惑,谢谢啦!

Lihui Liu1:

回复 mangui zhang:

非常感谢,通过查找,我们发现应该是控制DSP的FPGA虚焊了,所以导致DSP在不断的复位~

TI中文支持网

TI中文支持网