您好:

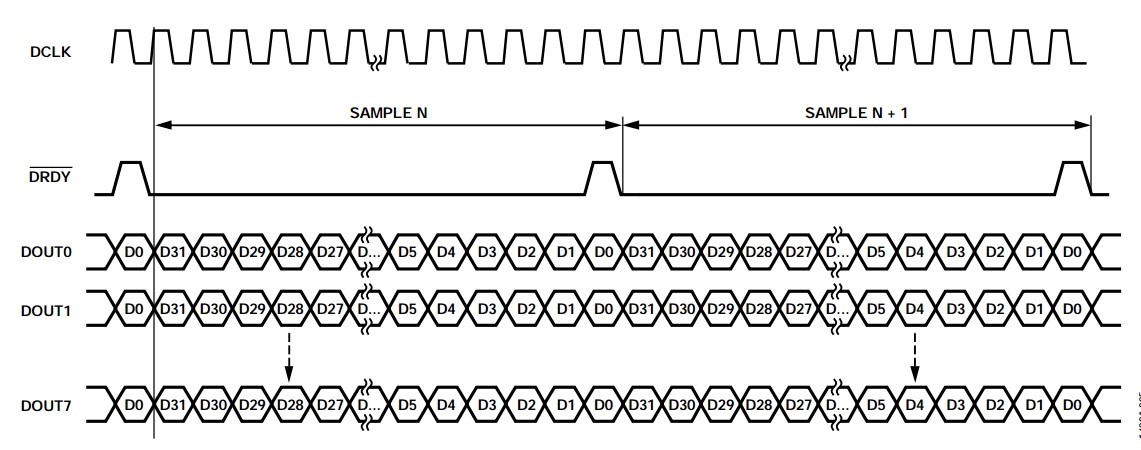

我们想用TMS320C28341,想请教一下是否支持以下数据获取方式:其中DCLK为AD(作为主芯片)输出时钟,DCLK为8.192Mbps。

另外,是否可以增加或减少输出管脚个数? 比如,只使用DOUT0,而DCLD为65.536Mbps(同SPI);

或者,使用DOUT0-DOUT1,DCLK为32.768Mbps。

mangui zhang:SPI的话AD的随路时钟就给spi当时钟用D0送入到spi的数据spi配置为slave模式。重点是ready信号这个直接确保数据的一包接收完成。看看能不能和使能完美结合 不行看是否用中断

TI中文支持网

TI中文支持网