CCS是v9.2 版本的,板子是TI的Launchxl-F28069M,在目标配置文件中配置XDS100V2与TMS320F28069之后,测试test connection,出现如下问题:

请问怎么解决?

[Start: Texas Instruments XDS100v2 USB Debug Probe_0]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

—–[Print the board config pathname(s)]————————————

C:\Users\ADMINI~1\AppData\Local\TEXASI~1\

CCS\ccs920\1\0\BrdDat\testBoard.dat

—–[Print the reset-command software log-file]—————————–

This utility has selected a 100- or 510-class product.

This utility will load the adapter 'jioserdesusb.dll'.

The library build date was 'Aug 26 2019'.

The library build time was '13:34:49'.

The library package version is '8.3.0.00003'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '4' (0x00000004).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

—–[Print the reset-command hardware log-file]—————————–

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the FTDI FT2232 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for FTDI FT2232 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

—–[The log-file for the JTAG TCLK output generated from the PLL]———-

There is no hardware for programming the JTAG TCLK frequency.

—–[Measure the source and frequency of the final JTAG TCLKR input]——–

There is no hardware for measuring the JTAG TCLK frequency.

—–[Perform the standard path-length test on the JTAG IR and DR]———–

This path-length test uses blocks of 64 32-bit words.

The test for the JTAG IR instruction path-length failed.

The JTAG IR instruction scan-path is stuck-at-ones.

The test for the JTAG DR bypass path-length failed.

The JTAG DR bypass scan-path is stuck-at-ones.

—–[Perform the Integrity scan-test on the JTAG IR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG IR Integrity scan-test has failed.

—–[Perform the Integrity scan-test on the JTAG DR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG DR Integrity scan-test has failed.

[End: Texas Instruments XDS100v2 USB Debug Probe_0]

mangui zhang:

1.确定一下设备管理器下是否能看到仿真器的两个设备

2.确保复位、电源是否正常,最好看看clkout有没有输出

CCS是v9.2 版本的,板子是TI的Launchxl-F28069M,在目标配置文件中配置XDS100V2与TMS320F28069之后,测试test connection,出现如下问题:

请问怎么解决?

[Start: Texas Instruments XDS100v2 USB Debug Probe_0]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

—–[Print the board config pathname(s)]————————————

C:\Users\ADMINI~1\AppData\Local\TEXASI~1\

CCS\ccs920\1\0\BrdDat\testBoard.dat

—–[Print the reset-command software log-file]—————————–

This utility has selected a 100- or 510-class product.

This utility will load the adapter 'jioserdesusb.dll'.

The library build date was 'Aug 26 2019'.

The library build time was '13:34:49'.

The library package version is '8.3.0.00003'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '4' (0x00000004).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

—–[Print the reset-command hardware log-file]—————————–

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the FTDI FT2232 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for FTDI FT2232 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

—–[The log-file for the JTAG TCLK output generated from the PLL]———-

There is no hardware for programming the JTAG TCLK frequency.

—–[Measure the source and frequency of the final JTAG TCLKR input]——–

There is no hardware for measuring the JTAG TCLK frequency.

—–[Perform the standard path-length test on the JTAG IR and DR]———–

This path-length test uses blocks of 64 32-bit words.

The test for the JTAG IR instruction path-length failed.

The JTAG IR instruction scan-path is stuck-at-ones.

The test for the JTAG DR bypass path-length failed.

The JTAG DR bypass scan-path is stuck-at-ones.

—–[Perform the Integrity scan-test on the JTAG IR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG IR Integrity scan-test has failed.

—–[Perform the Integrity scan-test on the JTAG DR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG DR Integrity scan-test has failed.

[End: Texas Instruments XDS100v2 USB Debug Probe_0]

Susan Yang:您先用uniflash试一下能不能连上

若是可以的话,就是CCS配置的相关问题

CCS是v9.2 版本的,板子是TI的Launchxl-F28069M,在目标配置文件中配置XDS100V2与TMS320F28069之后,测试test connection,出现如下问题:

请问怎么解决?

[Start: Texas Instruments XDS100v2 USB Debug Probe_0]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

—–[Print the board config pathname(s)]————————————

C:\Users\ADMINI~1\AppData\Local\TEXASI~1\

CCS\ccs920\1\0\BrdDat\testBoard.dat

—–[Print the reset-command software log-file]—————————–

This utility has selected a 100- or 510-class product.

This utility will load the adapter 'jioserdesusb.dll'.

The library build date was 'Aug 26 2019'.

The library build time was '13:34:49'.

The library package version is '8.3.0.00003'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '4' (0x00000004).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

—–[Print the reset-command hardware log-file]—————————–

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the FTDI FT2232 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for FTDI FT2232 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

—–[The log-file for the JTAG TCLK output generated from the PLL]———-

There is no hardware for programming the JTAG TCLK frequency.

—–[Measure the source and frequency of the final JTAG TCLKR input]——–

There is no hardware for measuring the JTAG TCLK frequency.

—–[Perform the standard path-length test on the JTAG IR and DR]———–

This path-length test uses blocks of 64 32-bit words.

The test for the JTAG IR instruction path-length failed.

The JTAG IR instruction scan-path is stuck-at-ones.

The test for the JTAG DR bypass path-length failed.

The JTAG DR bypass scan-path is stuck-at-ones.

—–[Perform the Integrity scan-test on the JTAG IR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG IR Integrity scan-test has failed.

—–[Perform the Integrity scan-test on the JTAG DR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG DR Integrity scan-test has failed.

[End: Texas Instruments XDS100v2 USB Debug Probe_0]

yingying fu:

回复 Susan Yang:

你好,我用uniflash 试了一下,出现问题:

[2019/11/25 上午10:19:29] [ERROR] C28xx: Error connecting to the target: (Error -1135 @ 0x0) The debug probe reported an error. Confirm debug probe configuration and connections, reset the debug probe, and retry the operation. (Emulation package 8.3.0.00003)。

这是什么情况,我也在设备管理器上可以看到仿真器的两个设备,电源也能检测到5V和3.3V电压,复位也正常。这是什么问题,有什么解决办法?谢谢

CCS是v9.2 版本的,板子是TI的Launchxl-F28069M,在目标配置文件中配置XDS100V2与TMS320F28069之后,测试test connection,出现如下问题:

请问怎么解决?

[Start: Texas Instruments XDS100v2 USB Debug Probe_0]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

—–[Print the board config pathname(s)]————————————

C:\Users\ADMINI~1\AppData\Local\TEXASI~1\

CCS\ccs920\1\0\BrdDat\testBoard.dat

—–[Print the reset-command software log-file]—————————–

This utility has selected a 100- or 510-class product.

This utility will load the adapter 'jioserdesusb.dll'.

The library build date was 'Aug 26 2019'.

The library build time was '13:34:49'.

The library package version is '8.3.0.00003'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '4' (0x00000004).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

—–[Print the reset-command hardware log-file]—————————–

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the FTDI FT2232 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for FTDI FT2232 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

—–[The log-file for the JTAG TCLK output generated from the PLL]———-

There is no hardware for programming the JTAG TCLK frequency.

—–[Measure the source and frequency of the final JTAG TCLKR input]——–

There is no hardware for measuring the JTAG TCLK frequency.

—–[Perform the standard path-length test on the JTAG IR and DR]———–

This path-length test uses blocks of 64 32-bit words.

The test for the JTAG IR instruction path-length failed.

The JTAG IR instruction scan-path is stuck-at-ones.

The test for the JTAG DR bypass path-length failed.

The JTAG DR bypass scan-path is stuck-at-ones.

—–[Perform the Integrity scan-test on the JTAG IR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG IR Integrity scan-test has failed.

—–[Perform the Integrity scan-test on the JTAG DR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG DR Integrity scan-test has failed.

[End: Texas Instruments XDS100v2 USB Debug Probe_0]

Susan Yang:

回复 yingying fu:

yingying fu我也在设备管理器上可以看到仿真器的两个设备

请您给出相关的截图,谢谢

CCS是v9.2 版本的,板子是TI的Launchxl-F28069M,在目标配置文件中配置XDS100V2与TMS320F28069之后,测试test connection,出现如下问题:

请问怎么解决?

[Start: Texas Instruments XDS100v2 USB Debug Probe_0]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

—–[Print the board config pathname(s)]————————————

C:\Users\ADMINI~1\AppData\Local\TEXASI~1\

CCS\ccs920\1\0\BrdDat\testBoard.dat

—–[Print the reset-command software log-file]—————————–

This utility has selected a 100- or 510-class product.

This utility will load the adapter 'jioserdesusb.dll'.

The library build date was 'Aug 26 2019'.

The library build time was '13:34:49'.

The library package version is '8.3.0.00003'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '4' (0x00000004).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

—–[Print the reset-command hardware log-file]—————————–

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the FTDI FT2232 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for FTDI FT2232 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

—–[The log-file for the JTAG TCLK output generated from the PLL]———-

There is no hardware for programming the JTAG TCLK frequency.

—–[Measure the source and frequency of the final JTAG TCLKR input]——–

There is no hardware for measuring the JTAG TCLK frequency.

—–[Perform the standard path-length test on the JTAG IR and DR]———–

This path-length test uses blocks of 64 32-bit words.

The test for the JTAG IR instruction path-length failed.

The JTAG IR instruction scan-path is stuck-at-ones.

The test for the JTAG DR bypass path-length failed.

The JTAG DR bypass scan-path is stuck-at-ones.

—–[Perform the Integrity scan-test on the JTAG IR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG IR Integrity scan-test has failed.

—–[Perform the Integrity scan-test on the JTAG DR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG DR Integrity scan-test has failed.

[End: Texas Instruments XDS100v2 USB Debug Probe_0]

yingying fu:

回复 Susan Yang:

截图如下所示测试连接1-配置截图.docx

CCS是v9.2 版本的,板子是TI的Launchxl-F28069M,在目标配置文件中配置XDS100V2与TMS320F28069之后,测试test connection,出现如下问题:

请问怎么解决?

[Start: Texas Instruments XDS100v2 USB Debug Probe_0]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

—–[Print the board config pathname(s)]————————————

C:\Users\ADMINI~1\AppData\Local\TEXASI~1\

CCS\ccs920\1\0\BrdDat\testBoard.dat

—–[Print the reset-command software log-file]—————————–

This utility has selected a 100- or 510-class product.

This utility will load the adapter 'jioserdesusb.dll'.

The library build date was 'Aug 26 2019'.

The library build time was '13:34:49'.

The library package version is '8.3.0.00003'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '4' (0x00000004).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

—–[Print the reset-command hardware log-file]—————————–

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the FTDI FT2232 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for FTDI FT2232 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

—–[The log-file for the JTAG TCLK output generated from the PLL]———-

There is no hardware for programming the JTAG TCLK frequency.

—–[Measure the source and frequency of the final JTAG TCLKR input]——–

There is no hardware for measuring the JTAG TCLK frequency.

—–[Perform the standard path-length test on the JTAG IR and DR]———–

This path-length test uses blocks of 64 32-bit words.

The test for the JTAG IR instruction path-length failed.

The JTAG IR instruction scan-path is stuck-at-ones.

The test for the JTAG DR bypass path-length failed.

The JTAG DR bypass scan-path is stuck-at-ones.

—–[Perform the Integrity scan-test on the JTAG IR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG IR Integrity scan-test has failed.

—–[Perform the Integrity scan-test on the JTAG DR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG DR Integrity scan-test has failed.

[End: Texas Instruments XDS100v2 USB Debug Probe_0]

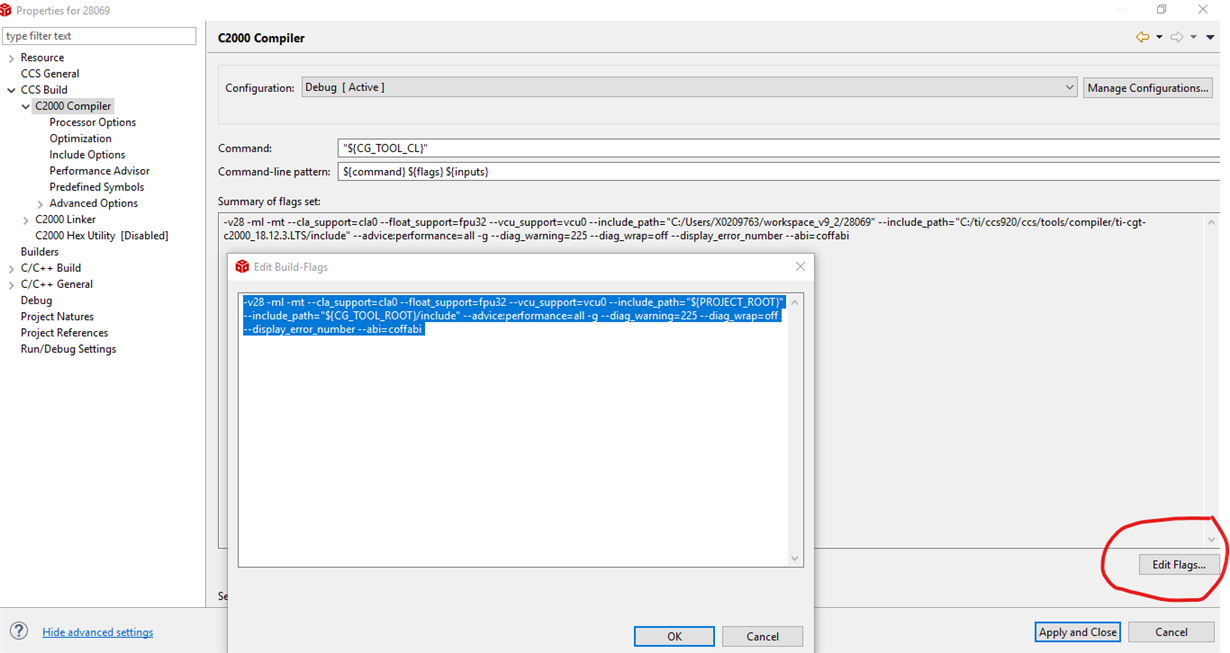

Susan Yang:

回复 yingying fu:

在此去掉 –cdebug_asm_data

配置的话,看着没有什么问题

有没有使用uniflash试一下?

CCS是v9.2 版本的,板子是TI的Launchxl-F28069M,在目标配置文件中配置XDS100V2与TMS320F28069之后,测试test connection,出现如下问题:

请问怎么解决?

[Start: Texas Instruments XDS100v2 USB Debug Probe_0]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

—–[Print the board config pathname(s)]————————————

C:\Users\ADMINI~1\AppData\Local\TEXASI~1\

CCS\ccs920\1\0\BrdDat\testBoard.dat

—–[Print the reset-command software log-file]—————————–

This utility has selected a 100- or 510-class product.

This utility will load the adapter 'jioserdesusb.dll'.

The library build date was 'Aug 26 2019'.

The library build time was '13:34:49'.

The library package version is '8.3.0.00003'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '4' (0x00000004).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

—–[Print the reset-command hardware log-file]—————————–

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the FTDI FT2232 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for FTDI FT2232 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

—–[The log-file for the JTAG TCLK output generated from the PLL]———-

There is no hardware for programming the JTAG TCLK frequency.

—–[Measure the source and frequency of the final JTAG TCLKR input]——–

There is no hardware for measuring the JTAG TCLK frequency.

—–[Perform the standard path-length test on the JTAG IR and DR]———–

This path-length test uses blocks of 64 32-bit words.

The test for the JTAG IR instruction path-length failed.

The JTAG IR instruction scan-path is stuck-at-ones.

The test for the JTAG DR bypass path-length failed.

The JTAG DR bypass scan-path is stuck-at-ones.

—–[Perform the Integrity scan-test on the JTAG IR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG IR Integrity scan-test has failed.

—–[Perform the Integrity scan-test on the JTAG DR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG DR Integrity scan-test has failed.

[End: Texas Instruments XDS100v2 USB Debug Probe_0]

yingying fu:

回复 Susan Yang:

测试连接2-截图.docx

CCS是v9.2 版本的,板子是TI的Launchxl-F28069M,在目标配置文件中配置XDS100V2与TMS320F28069之后,测试test connection,出现如下问题:

请问怎么解决?

[Start: Texas Instruments XDS100v2 USB Debug Probe_0]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

—–[Print the board config pathname(s)]————————————

C:\Users\ADMINI~1\AppData\Local\TEXASI~1\

CCS\ccs920\1\0\BrdDat\testBoard.dat

—–[Print the reset-command software log-file]—————————–

This utility has selected a 100- or 510-class product.

This utility will load the adapter 'jioserdesusb.dll'.

The library build date was 'Aug 26 2019'.

The library build time was '13:34:49'.

The library package version is '8.3.0.00003'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '4' (0x00000004).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

—–[Print the reset-command hardware log-file]—————————–

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the FTDI FT2232 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for FTDI FT2232 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

—–[The log-file for the JTAG TCLK output generated from the PLL]———-

There is no hardware for programming the JTAG TCLK frequency.

—–[Measure the source and frequency of the final JTAG TCLKR input]——–

There is no hardware for measuring the JTAG TCLK frequency.

—–[Perform the standard path-length test on the JTAG IR and DR]———–

This path-length test uses blocks of 64 32-bit words.

The test for the JTAG IR instruction path-length failed.

The JTAG IR instruction scan-path is stuck-at-ones.

The test for the JTAG DR bypass path-length failed.

The JTAG DR bypass scan-path is stuck-at-ones.

—–[Perform the Integrity scan-test on the JTAG IR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG IR Integrity scan-test has failed.

—–[Perform the Integrity scan-test on the JTAG DR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG DR Integrity scan-test has failed.

[End: Texas Instruments XDS100v2 USB Debug Probe_0]

Susan Yang:

回复 yingying fu:

您只需要去掉 –cdebug_asm_data 就可以了 因为现在不支持了

关于uniflash的错误,查看

software-dl.ti.com/…/ccsv7_debugging_jtag_connectivity_issues.html

您换个板子试试吧 感觉您这块板子硬件有问题

CCS是v9.2 版本的,板子是TI的Launchxl-F28069M,在目标配置文件中配置XDS100V2与TMS320F28069之后,测试test connection,出现如下问题:

请问怎么解决?

[Start: Texas Instruments XDS100v2 USB Debug Probe_0]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

—–[Print the board config pathname(s)]————————————

C:\Users\ADMINI~1\AppData\Local\TEXASI~1\

CCS\ccs920\1\0\BrdDat\testBoard.dat

—–[Print the reset-command software log-file]—————————–

This utility has selected a 100- or 510-class product.

This utility will load the adapter 'jioserdesusb.dll'.

The library build date was 'Aug 26 2019'.

The library build time was '13:34:49'.

The library package version is '8.3.0.00003'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '4' (0x00000004).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

—–[Print the reset-command hardware log-file]—————————–

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the FTDI FT2232 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for FTDI FT2232 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

—–[The log-file for the JTAG TCLK output generated from the PLL]———-

There is no hardware for programming the JTAG TCLK frequency.

—–[Measure the source and frequency of the final JTAG TCLKR input]——–

There is no hardware for measuring the JTAG TCLK frequency.

—–[Perform the standard path-length test on the JTAG IR and DR]———–

This path-length test uses blocks of 64 32-bit words.

The test for the JTAG IR instruction path-length failed.

The JTAG IR instruction scan-path is stuck-at-ones.

The test for the JTAG DR bypass path-length failed.

The JTAG DR bypass scan-path is stuck-at-ones.

—–[Perform the Integrity scan-test on the JTAG IR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG IR Integrity scan-test has failed.

—–[Perform the Integrity scan-test on the JTAG DR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG DR Integrity scan-test has failed.

[End: Texas Instruments XDS100v2 USB Debug Probe_0]

yingying fu:

回复 Susan Yang:

test connection测试成功的条件都有什么?(比如COM口,驱动,配置等还需要什么)谢谢

CCS是v9.2 版本的,板子是TI的Launchxl-F28069M,在目标配置文件中配置XDS100V2与TMS320F28069之后,测试test connection,出现如下问题:

请问怎么解决?

[Start: Texas Instruments XDS100v2 USB Debug Probe_0]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

—–[Print the board config pathname(s)]————————————

C:\Users\ADMINI~1\AppData\Local\TEXASI~1\

CCS\ccs920\1\0\BrdDat\testBoard.dat

—–[Print the reset-command software log-file]—————————–

This utility has selected a 100- or 510-class product.

This utility will load the adapter 'jioserdesusb.dll'.

The library build date was 'Aug 26 2019'.

The library build time was '13:34:49'.

The library package version is '8.3.0.00003'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '4' (0x00000004).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

—–[Print the reset-command hardware log-file]—————————–

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the FTDI FT2232 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for FTDI FT2232 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

—–[The log-file for the JTAG TCLK output generated from the PLL]———-

There is no hardware for programming the JTAG TCLK frequency.

—–[Measure the source and frequency of the final JTAG TCLKR input]——–

There is no hardware for measuring the JTAG TCLK frequency.

—–[Perform the standard path-length test on the JTAG IR and DR]———–

This path-length test uses blocks of 64 32-bit words.

The test for the JTAG IR instruction path-length failed.

The JTAG IR instruction scan-path is stuck-at-ones.

The test for the JTAG DR bypass path-length failed.

The JTAG DR bypass scan-path is stuck-at-ones.

—–[Perform the Integrity scan-test on the JTAG IR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG IR Integrity scan-test has failed.

—–[Perform the Integrity scan-test on the JTAG DR]————————

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Test 2 Word 0: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 1: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 2: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 3: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 4: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 5: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 6: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

Test 2 Word 7: scanned out 0x00000000 and scanned in 0xFFFFFFFF.

The details of the first 8 errors have been provided.

The utility will now report only the count of failed tests.

Scan tests: 2, skipped: 0, failed: 1

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 2

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 3

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 4

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 5

Some of the values were corrupted – 83.3 percent.

The JTAG DR Integrity scan-test has failed.

[End: Texas Instruments XDS100v2 USB Debug Probe_0]

Susan Yang:

回复 yingying fu:

首先保证您的板子硬件没有问题,设备管理器能够正常识别您现在的设备,这个板子的话,不需要在CCS内特殊配置了,直接使用默认的就可以了

您现在uniflash连不上,根据错误提示很大概率是您的硬件问题,所以建议您若是可以的话,换一块试试

来确认是否是硬件本身的问题

TI中文支持网

TI中文支持网