将定时器2的PWM输出作为定时器4的时钟输入(硬链接)

GpioMuxRegs.GPAQUAL.all=0x0000;

GpioMuxRegs.GPBQUAL.all=0x0000;

问题:

将捕获到得定时器2的值作为低16位,捕获的定时器4的值作为高16位,发现当低16位捕获到得数据为0附近的较小值时(比如0或1)其高16位捕获到得值还没有加1,及还没有捕获到定时器2的进位!

请问这会是什么问题引起的!定时器对外部时钟除了GPBQUAL寄存器能滤波还有其他的滤波吗?

10#:

能否请将你的问题描述清楚一些?

你所谓的定时器是指Timer,还是ePWM模块?捕获功能是由ePWM,eCAP还是GPIO的外部中断实现的?

或者能不能直接说是硬件的哪几个PIN脚,软件如何设置,希望完成的功能是什么?

芯片内部能确定的是,每个GPIO口当复用为输入功能的其它外设如eCAP或外部中断时,都有QUAL的滤波,但再没有其它的了。

将定时器2的PWM输出作为定时器4的时钟输入(硬链接)

GpioMuxRegs.GPAQUAL.all=0x0000;

GpioMuxRegs.GPBQUAL.all=0x0000;

问题:

将捕获到得定时器2的值作为低16位,捕获的定时器4的值作为高16位,发现当低16位捕获到得数据为0附近的较小值时(比如0或1)其高16位捕获到得值还没有加1,及还没有捕获到定时器2的进位!

请问这会是什么问题引起的!定时器对外部时钟除了GPBQUAL寄存器能滤波还有其他的滤波吗?

QIANG WANG1:

回复 10#:

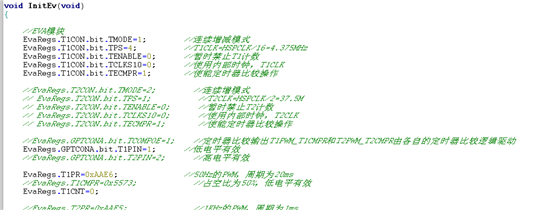

我使用的是2812芯片,使用CAP1和CAP5捕获上升沿,CAP1使用定时器2,CAP5使用定时器4,定时器2的周期为0x7FFF,比较寄存器为0x4000,定时器2使用60M的内部时钟,定时器4的时钟使用外部时钟,及72脚TCLKINB

将T2PWM(104脚)和TCLKINB连接,想利用上述方案实现一个31位的捕获!及当CAP5进入捕获中断时同时读出其16位和CAP1的低15位!但实际情况是当CAP1的捕获值为0附近的数值时,CAP5还没有捕获到此次定时器2的进位!及捕获值差了32678左右!

将定时器2的PWM输出作为定时器4的时钟输入(硬链接)

GpioMuxRegs.GPAQUAL.all=0x0000;

GpioMuxRegs.GPBQUAL.all=0x0000;

问题:

将捕获到得定时器2的值作为低16位,捕获的定时器4的值作为高16位,发现当低16位捕获到得数据为0附近的较小值时(比如0或1)其高16位捕获到得值还没有加1,及还没有捕获到定时器2的进位!

请问这会是什么问题引起的!定时器对外部时钟除了GPBQUAL寄存器能滤波还有其他的滤波吗?

Yanming Luo:

这个是由于T2PWM输出作为CLOCK提供给timer_4时,时钟输入的同步引起的。所以如果你采用这种方法,就可能会有一个时钟的误差为60M Clock的32768,即为T2PWM的一个脉冲输出。

其实你可以用以下方法来实现同样的功能:

Timer_2的周期设为0xFFFF,并允许CAP和Timer_2的周期中断,在CAP中断中看timer_2中断进入的次数(其为高16位),CAP的计数寄存器为低16位。

TI中文支持网

TI中文支持网