分享一个28M35数据交换的机制,希望对双核学习的兄弟有帮助:

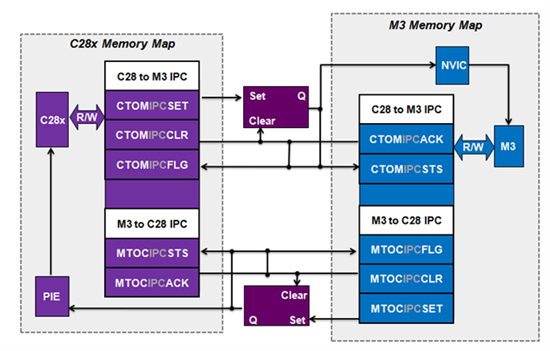

流程图如下:

过程分析如下:

中断IPC通信流程:

下面是一个基于中断方式IPC应用案例,描述一个M3对C2K的IPC请求,采用中断方式请求,中断源利用到C2K 的MTOCPICINT1。

- M3主核对MTOCIPCSET寄存器的第0位写1,C2K PIE中断会产品一个MTOCIPCINT0类型中断。

- MTOCIPCFIL寄存器和MTOCIPCSTS寄存器的第0位自动置1,C28进入IPC中断处理函数,C2K开始加载定义好的数据到共享RAM中或者CTOM RAM中。

- C2K写1到MTOCIPCACK寄存器的第0为,MTOIPC请求清除MTOCIPC中断。

- M3循环等待MTOCIPCFLG寄存器第0位,知道该位状态变为0。MTOCIPCFLG位为1表示C2K中断没有被相应,MTOCIPCFLG相应为变为0表示,C2K中断已经响应,可以读取C2K共享的RAM信息。

标示位等待IPC通信流程:

下面是一个标示位等待方式IPC应用案例,描述一个C2K采样非中断方式接共享数据,让M3主核可以读取数据。

- C2K对CTOMIPCSET寄存器第5位置1,暗示告诉M3继续执行指令的M3可以读取C2K已经完成共享的RAM数据。

- M3继续执行指令,等M3希望得到C2K是否有共享的数据时,M3读取CTOMIPCSTS寄存器值,当M3发现CTOMIPCSTS状态寄存器的第5位为1时,M3开始读取共享RAM数据。

- M3完成数据读取之后,M3置位CTOMIPCACK寄存器第五位,清除CTOMIPCSTS状态值。

- 当C2K CPU检测到CTOMIPCFLG第五位为1时,说明M3没有或者正在使用共享SRAM,但当CPU检测到CTOMIPCFLG第五位为0时,表示M3已经完成共享数据的操作。C2K可以继续其任务处理。

O(∩_∩)O~

TI中文支持网

TI中文支持网