第一次做这方面东西,很多地方请前辈多多指教一下。我要用2812驱动一个外置的AD芯片,ADS805。看了一下数据表,ADS805是每6个时钟采集一个数据。速度可以达到20MHz。现在我常使用CPU定时器产生时钟,PRDH:PRD赋值14,TDDRH:TDDR赋值0,这样理论计算结果定时周期应该是(14+1)*(0+1)*(1/150)=100ns,当然,我这里PLL已经把SYSCLK设置为150MHz了。这样设置定时器后,每次定时器中断让某GPIO(经电平转换连接在ADS805的CLK引脚的IO口)的值变化一次,即1010这样的变化,在示波器上看到的图像显示变化一次时间为250ns~300ns的样子,经过调整PRDH:PRD之后,发现当给其赋值149,74(这俩数方便计算),等比较大的值时,定时器控制IO口输出的波形很正常,和计算结果吻合。但当PRDH:PRD赋值比较小,如40以内,GPIO输出波形就卡在250ns的样子,不能再小了。 后怀疑是IO口输出速率的问题,但我试了赋值14,即理论计算值为100ns,实际输出值250ns的时候,经10次中断再输出到IO口,输出波形并不是理论计算的十倍,而是250ns的10倍,遂证明,依旧是CPU定时器的问题。

请问我CPU定时器该怎么调才能到250ns以内呢,目前我的采样要求大概是5Mhz(ADS805是20MHz的),所以1us内要通过2812输出的时钟数量是5*6=30个时钟信号。目前250ns变化一次,即周期为500ns(实测比这个还要大一些),也就是说目前1us只能输出不到2个完整时钟信号,这种情况很糟糕,会让AD的采样频率降低到几百Khz。

dirtwillfly:

没看出有什么问题。建议楼主提供下代码看看。

第一次做这方面东西,很多地方请前辈多多指教一下。我要用2812驱动一个外置的AD芯片,ADS805。看了一下数据表,ADS805是每6个时钟采集一个数据。速度可以达到20MHz。现在我常使用CPU定时器产生时钟,PRDH:PRD赋值14,TDDRH:TDDR赋值0,这样理论计算结果定时周期应该是(14+1)*(0+1)*(1/150)=100ns,当然,我这里PLL已经把SYSCLK设置为150MHz了。这样设置定时器后,每次定时器中断让某GPIO(经电平转换连接在ADS805的CLK引脚的IO口)的值变化一次,即1010这样的变化,在示波器上看到的图像显示变化一次时间为250ns~300ns的样子,经过调整PRDH:PRD之后,发现当给其赋值149,74(这俩数方便计算),等比较大的值时,定时器控制IO口输出的波形很正常,和计算结果吻合。但当PRDH:PRD赋值比较小,如40以内,GPIO输出波形就卡在250ns的样子,不能再小了。 后怀疑是IO口输出速率的问题,但我试了赋值14,即理论计算值为100ns,实际输出值250ns的时候,经10次中断再输出到IO口,输出波形并不是理论计算的十倍,而是250ns的10倍,遂证明,依旧是CPU定时器的问题。

请问我CPU定时器该怎么调才能到250ns以内呢,目前我的采样要求大概是5Mhz(ADS805是20MHz的),所以1us内要通过2812输出的时钟数量是5*6=30个时钟信号。目前250ns变化一次,即周期为500ns(实测比这个还要大一些),也就是说目前1us只能输出不到2个完整时钟信号,这种情况很糟糕,会让AD的采样频率降低到几百Khz。

Kui Jin:

回复 dirtwillfly:

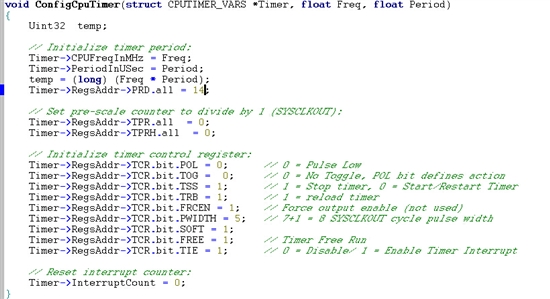

CPU定时器设置

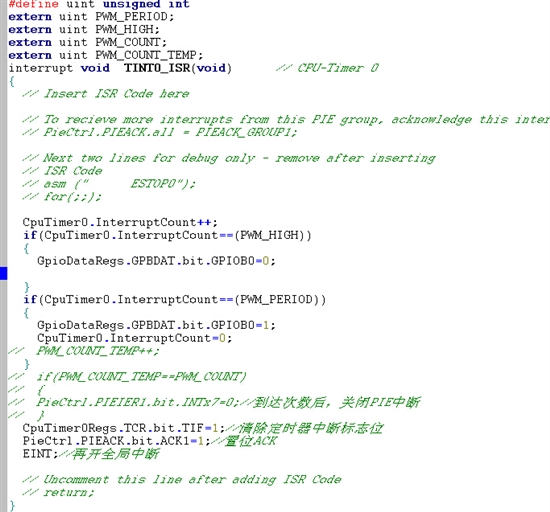

中断函数

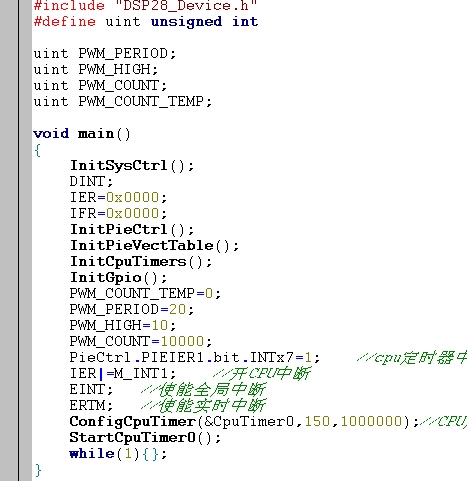

主函数

第一次做这方面东西,很多地方请前辈多多指教一下。我要用2812驱动一个外置的AD芯片,ADS805。看了一下数据表,ADS805是每6个时钟采集一个数据。速度可以达到20MHz。现在我常使用CPU定时器产生时钟,PRDH:PRD赋值14,TDDRH:TDDR赋值0,这样理论计算结果定时周期应该是(14+1)*(0+1)*(1/150)=100ns,当然,我这里PLL已经把SYSCLK设置为150MHz了。这样设置定时器后,每次定时器中断让某GPIO(经电平转换连接在ADS805的CLK引脚的IO口)的值变化一次,即1010这样的变化,在示波器上看到的图像显示变化一次时间为250ns~300ns的样子,经过调整PRDH:PRD之后,发现当给其赋值149,74(这俩数方便计算),等比较大的值时,定时器控制IO口输出的波形很正常,和计算结果吻合。但当PRDH:PRD赋值比较小,如40以内,GPIO输出波形就卡在250ns的样子,不能再小了。 后怀疑是IO口输出速率的问题,但我试了赋值14,即理论计算值为100ns,实际输出值250ns的时候,经10次中断再输出到IO口,输出波形并不是理论计算的十倍,而是250ns的10倍,遂证明,依旧是CPU定时器的问题。

请问我CPU定时器该怎么调才能到250ns以内呢,目前我的采样要求大概是5Mhz(ADS805是20MHz的),所以1us内要通过2812输出的时钟数量是5*6=30个时钟信号。目前250ns变化一次,即周期为500ns(实测比这个还要大一些),也就是说目前1us只能输出不到2个完整时钟信号,这种情况很糟糕,会让AD的采样频率降低到几百Khz。

Kui Jin:

回复 dirtwillfly:

请帮忙看一下吧·~~谢谢啦。

第一次做这方面东西,很多地方请前辈多多指教一下。我要用2812驱动一个外置的AD芯片,ADS805。看了一下数据表,ADS805是每6个时钟采集一个数据。速度可以达到20MHz。现在我常使用CPU定时器产生时钟,PRDH:PRD赋值14,TDDRH:TDDR赋值0,这样理论计算结果定时周期应该是(14+1)*(0+1)*(1/150)=100ns,当然,我这里PLL已经把SYSCLK设置为150MHz了。这样设置定时器后,每次定时器中断让某GPIO(经电平转换连接在ADS805的CLK引脚的IO口)的值变化一次,即1010这样的变化,在示波器上看到的图像显示变化一次时间为250ns~300ns的样子,经过调整PRDH:PRD之后,发现当给其赋值149,74(这俩数方便计算),等比较大的值时,定时器控制IO口输出的波形很正常,和计算结果吻合。但当PRDH:PRD赋值比较小,如40以内,GPIO输出波形就卡在250ns的样子,不能再小了。 后怀疑是IO口输出速率的问题,但我试了赋值14,即理论计算值为100ns,实际输出值250ns的时候,经10次中断再输出到IO口,输出波形并不是理论计算的十倍,而是250ns的10倍,遂证明,依旧是CPU定时器的问题。

请问我CPU定时器该怎么调才能到250ns以内呢,目前我的采样要求大概是5Mhz(ADS805是20MHz的),所以1us内要通过2812输出的时钟数量是5*6=30个时钟信号。目前250ns变化一次,即周期为500ns(实测比这个还要大一些),也就是说目前1us只能输出不到2个完整时钟信号,这种情况很糟糕,会让AD的采样频率降低到几百Khz。

mangui zhang:

我觉得不是定时器到不了。应该是GPIO的翻转速度达不到

建议你查看datasheet GPIO的最大翻转速度能到多少

不行的话建议你用PWM波输出口

TI中文支持网

TI中文支持网