程序开通1s PWM,再关断1s PWM,再开通,再关断,循环进行,在关断前将强制将A、B输入均拉低,偶尔会出现一路(A或B),拉不低情况,代码如下:

//下面为关断PWM

EPwm2Regs.AQSFRC.bit.ACTSFA= 1;

EPwm2Regs.AQSFRC.bit.ACTSFB= 1;

EPwm2Regs.AQSFRC.bit.OTSFA = 1;

EPwm2Regs.AQSFRC.bit.OTSFB= 1;

g_dTBPRD = EPWM2_TIMER_TBPRD;

g_dCMPB = EPWM2_MIN_CMPB;

g_dCMPA = EPWM2_MIN_CMPA ;

EPwm2Regs.TBPRD =g_dTBPRD; //600; // Set timer period 801 TBCLKs

EPwm2Regs.CMPA.half.CMPA = g_dCMPA;//324;//; // Set compare A value

EPwm2Regs.CMPB = g_dCMPB;//276;//;

EALLOW;//关断PWM

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0;

EDIS;

//下面为开通PWM

EALLOW;SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1;

EDIS;

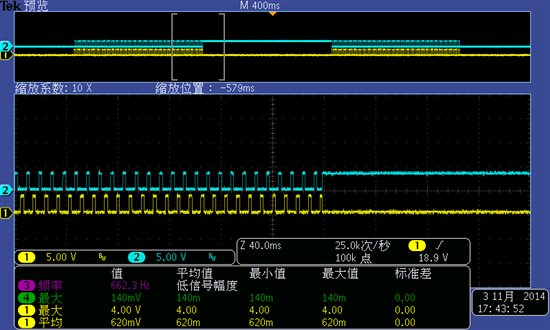

//图如下

囧:

你这样的关断方式是一种不可靠的关断方法,只是通过去掉PWM模块的时钟来禁止PWM的时基不计数,所以去掉时钟瞬间不知道PWM输出的当前状态,建议使用软件触发Trip Zone的方法强迫PWM高或者低,这样是可靠的控制关断电平的方法。

程序开通1s PWM,再关断1s PWM,再开通,再关断,循环进行,在关断前将强制将A、B输入均拉低,偶尔会出现一路(A或B),拉不低情况,代码如下:

//下面为关断PWM

EPwm2Regs.AQSFRC.bit.ACTSFA= 1;

EPwm2Regs.AQSFRC.bit.ACTSFB= 1;

EPwm2Regs.AQSFRC.bit.OTSFA = 1;

EPwm2Regs.AQSFRC.bit.OTSFB= 1;

g_dTBPRD = EPWM2_TIMER_TBPRD;

g_dCMPB = EPWM2_MIN_CMPB;

g_dCMPA = EPWM2_MIN_CMPA ;

EPwm2Regs.TBPRD =g_dTBPRD; //600; // Set timer period 801 TBCLKs

EPwm2Regs.CMPA.half.CMPA = g_dCMPA;//324;//; // Set compare A value

EPwm2Regs.CMPB = g_dCMPB;//276;//;

EALLOW;//关断PWM

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0;

EDIS;

//下面为开通PWM

EALLOW;SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1;

EDIS;

//图如下

Mak he:

回复 囧:

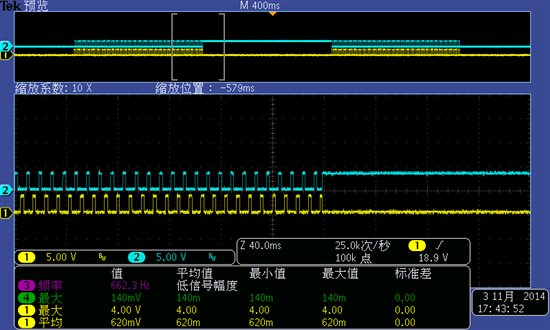

你说的是下面这种方式开通与关断,我在使用过程中关断是没有问题,开通时第一个周期经常出现不同的周期的PWM波,感觉是随机的,不知道是什么原因?

//初始化设置

EALLOW; //===========================================================================// TZA events can force EPWMxA// TZB events can force EPWMxB EPwm2Regs.TZCTL.bit.TZA = TZ_FORCE_LO; // EPWM1A will go low //故障产生时的保护 EPwm2Regs.TZCTL.bit.TZB = TZ_FORCE_LO; // EPWM1B will go low EPwm2Regs.TZFRC.bit.OST = 1; // Turn off the PWM

EDIS;

//开通PWM

#define mPWM2_ON() { EALLOW; \ EPwm2Regs.TZCLR.bit.OST = 1; \ EDIS;}

//关断PWM#define mPWM2_OFF() {EALLOW; \ EPwm2Regs.TZFRC.bit.OST = 1; \ EDIS; }

TI中文支持网

TI中文支持网