又有问题得麻烦热心的坛友们了,我写了个2812的外部ram测试代码。

xintf.c内配置如下:

void InitXintf(void)

{

// #if F2812

// Example of chaning the timing of XINTF Zones.

// Note acutal values should be based on the hardware // attached to the zone – timings presented here are // for example purposes.

// All Zones———————————

// Timing for all zones based on XTIMCLK = SYSCLKOUT

XintfRegs.XINTCNF2.bit.XTIMCLK = 0;

// No write buffering

XintfRegs.XINTCNF2.bit.WRBUFF = 0;

// XCLKOUT is enabled

XintfRegs.XINTCNF2.bit.CLKOFF = 0;

// XCLKOUT = XTIMCLK/2

XintfRegs.XINTCNF2.bit.CLKMODE = 1; //XCLK=75MHz

// Zone 6:

// Change write access lead active trail timing

// When using ready, ACTIVE must be 1 or greater

// Lead must always be 1 or greater

// Use timings based on SYSCLKOUT = XTIMCLK

XintfRegs.XTIMING6.bit.USEREADY=0;

XintfRegs.XTIMING6.bit.XSIZE=3;

XintfRegs.XTIMING6.bit.XWRTRAIL = 1;

XintfRegs.XTIMING6.bit.XWRACTIVE = 2;

XintfRegs.XTIMING6.bit.XWRLEAD = 1;

XintfRegs.XTIMING6.bit.XRDLEAD = 1;

XintfRegs.XTIMING6.bit.XRDACTIVE = 2;

XintfRegs.XTIMING6.bit.XRDTRAIL = 1;

//Not double lead/active/trail for Zone 6

XintfRegs.XTIMING6.bit.X2TIMING = 0; //时钟不翻倍

// Zone 6 is slow, so add additional BCYC cycles when ever switching

// from Zone 6 to another Zone. This will help avoid

// bus contention.

XintfRegs.XBANK.bit.BCYC = 2;

XintfRegs.XBANK.bit.BANK = 6;

// #endif

} main函数中每次往外部RAM写16K数据,写完后将一个GPIO翻转。现在得到的结果是按上述void InitXintf(void)配置GPIO口的方波只有163Hz左右,换算过来外部RAM写入速度只有2.8MHz左右。但是按上述配置理论上应该是(150MHz/2)/(1+2+1)=18.75MHz才对吧。而且我把XWRTRAIL、XWRACTIVE、XWRLEAD这三个时间分别设为1,1,1时,GPIO输出方波频率也只增加到176Hz,而如果改为3、7、3则方波为127Hz。这和手册上说的不符合啊,有哪位坛友知道问题出在哪里吗?谢谢赐教

minjie yuan1:

帖子里有点小错误,最高频率应该是6MHz左右,还是远远低于理论速度。用示波器观察CE和WE波形后,发现驱动脉冲的确只有这么点,而且换买过来的开发板测试也是一样的情况,所以肯定是程序除了问题。可是我是按照TI官方例程来配置的啊,我照着例程run_from_xintf中的顺序重新配置了结果还是一样。不解…

又有问题得麻烦热心的坛友们了,我写了个2812的外部ram测试代码。

xintf.c内配置如下:

void InitXintf(void)

{

// #if F2812

// Example of chaning the timing of XINTF Zones.

// Note acutal values should be based on the hardware // attached to the zone – timings presented here are // for example purposes.

// All Zones———————————

// Timing for all zones based on XTIMCLK = SYSCLKOUT

XintfRegs.XINTCNF2.bit.XTIMCLK = 0;

// No write buffering

XintfRegs.XINTCNF2.bit.WRBUFF = 0;

// XCLKOUT is enabled

XintfRegs.XINTCNF2.bit.CLKOFF = 0;

// XCLKOUT = XTIMCLK/2

XintfRegs.XINTCNF2.bit.CLKMODE = 1; //XCLK=75MHz

// Zone 6:

// Change write access lead active trail timing

// When using ready, ACTIVE must be 1 or greater

// Lead must always be 1 or greater

// Use timings based on SYSCLKOUT = XTIMCLK

XintfRegs.XTIMING6.bit.USEREADY=0;

XintfRegs.XTIMING6.bit.XSIZE=3;

XintfRegs.XTIMING6.bit.XWRTRAIL = 1;

XintfRegs.XTIMING6.bit.XWRACTIVE = 2;

XintfRegs.XTIMING6.bit.XWRLEAD = 1;

XintfRegs.XTIMING6.bit.XRDLEAD = 1;

XintfRegs.XTIMING6.bit.XRDACTIVE = 2;

XintfRegs.XTIMING6.bit.XRDTRAIL = 1;

//Not double lead/active/trail for Zone 6

XintfRegs.XTIMING6.bit.X2TIMING = 0; //时钟不翻倍

// Zone 6 is slow, so add additional BCYC cycles when ever switching

// from Zone 6 to another Zone. This will help avoid

// bus contention.

XintfRegs.XBANK.bit.BCYC = 2;

XintfRegs.XBANK.bit.BANK = 6;

// #endif

} main函数中每次往外部RAM写16K数据,写完后将一个GPIO翻转。现在得到的结果是按上述void InitXintf(void)配置GPIO口的方波只有163Hz左右,换算过来外部RAM写入速度只有2.8MHz左右。但是按上述配置理论上应该是(150MHz/2)/(1+2+1)=18.75MHz才对吧。而且我把XWRTRAIL、XWRACTIVE、XWRLEAD这三个时间分别设为1,1,1时,GPIO输出方波频率也只增加到176Hz,而如果改为3、7、3则方波为127Hz。这和手册上说的不符合啊,有哪位坛友知道问题出在哪里吗?谢谢赐教

mangui zhang:

回复 minjie yuan1:

外扩SDRAM的最高速度是多少啊 会不会是因为外扩芯片的影响?

还有一种可能就是XINTF接口配置的问题 不知道你现在问题出到哪儿了

又有问题得麻烦热心的坛友们了,我写了个2812的外部ram测试代码。

xintf.c内配置如下:

void InitXintf(void)

{

// #if F2812

// Example of chaning the timing of XINTF Zones.

// Note acutal values should be based on the hardware // attached to the zone – timings presented here are // for example purposes.

// All Zones———————————

// Timing for all zones based on XTIMCLK = SYSCLKOUT

XintfRegs.XINTCNF2.bit.XTIMCLK = 0;

// No write buffering

XintfRegs.XINTCNF2.bit.WRBUFF = 0;

// XCLKOUT is enabled

XintfRegs.XINTCNF2.bit.CLKOFF = 0;

// XCLKOUT = XTIMCLK/2

XintfRegs.XINTCNF2.bit.CLKMODE = 1; //XCLK=75MHz

// Zone 6:

// Change write access lead active trail timing

// When using ready, ACTIVE must be 1 or greater

// Lead must always be 1 or greater

// Use timings based on SYSCLKOUT = XTIMCLK

XintfRegs.XTIMING6.bit.USEREADY=0;

XintfRegs.XTIMING6.bit.XSIZE=3;

XintfRegs.XTIMING6.bit.XWRTRAIL = 1;

XintfRegs.XTIMING6.bit.XWRACTIVE = 2;

XintfRegs.XTIMING6.bit.XWRLEAD = 1;

XintfRegs.XTIMING6.bit.XRDLEAD = 1;

XintfRegs.XTIMING6.bit.XRDACTIVE = 2;

XintfRegs.XTIMING6.bit.XRDTRAIL = 1;

//Not double lead/active/trail for Zone 6

XintfRegs.XTIMING6.bit.X2TIMING = 0; //时钟不翻倍

// Zone 6 is slow, so add additional BCYC cycles when ever switching

// from Zone 6 to another Zone. This will help avoid

// bus contention.

XintfRegs.XBANK.bit.BCYC = 2;

XintfRegs.XBANK.bit.BANK = 6;

// #endif

} main函数中每次往外部RAM写16K数据,写完后将一个GPIO翻转。现在得到的结果是按上述void InitXintf(void)配置GPIO口的方波只有163Hz左右,换算过来外部RAM写入速度只有2.8MHz左右。但是按上述配置理论上应该是(150MHz/2)/(1+2+1)=18.75MHz才对吧。而且我把XWRTRAIL、XWRACTIVE、XWRLEAD这三个时间分别设为1,1,1时,GPIO输出方波频率也只增加到176Hz,而如果改为3、7、3则方波为127Hz。这和手册上说的不符合啊,有哪位坛友知道问题出在哪里吗?谢谢赐教

minjie yuan1:

回复 mangui zhang:

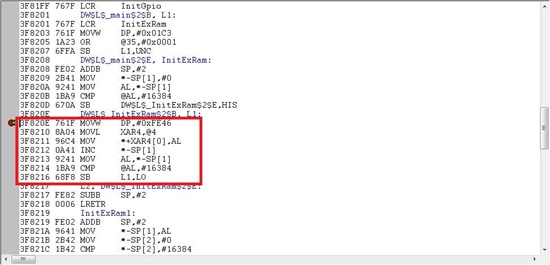

芯片没问题的,是10ns速度等级的。现在我怀疑是因为其他语句占了时间,现在的配置大概能实现8MHz左右的写入速度,我将C代码转换成汇编语句,发现每两次写数据到外部RAM之间要执行7条代码(用来产生外部RAM的写入地址和写入数据数计算),加上本身读写外部RAM需要3个时钟周期,也许就是因为这些原因造成了写入速度慢。

TI中文支持网

TI中文支持网