各位资深工程师,大家好!

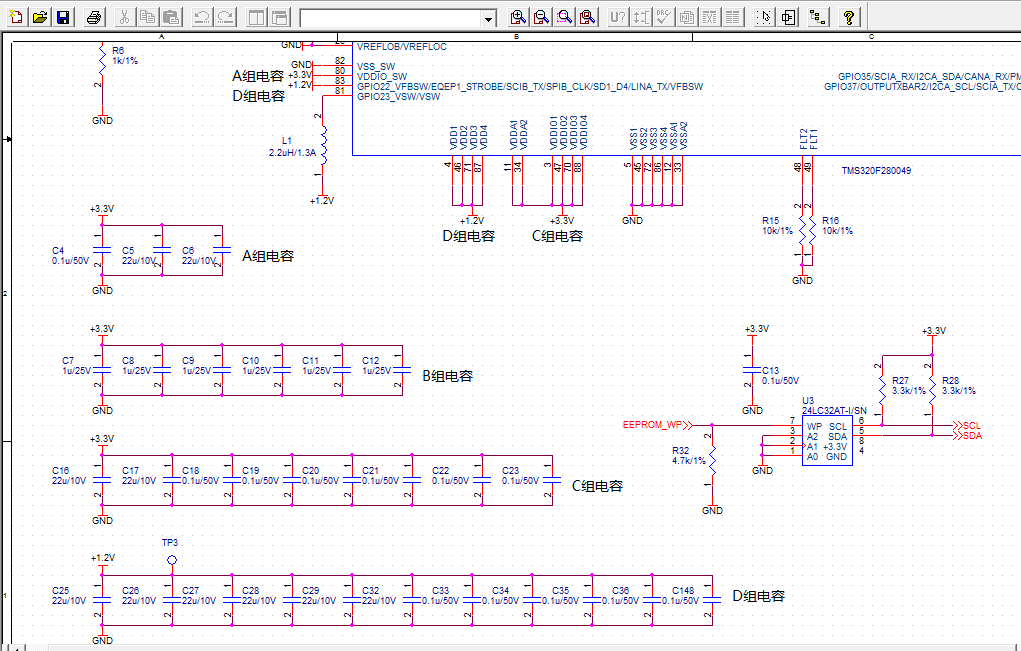

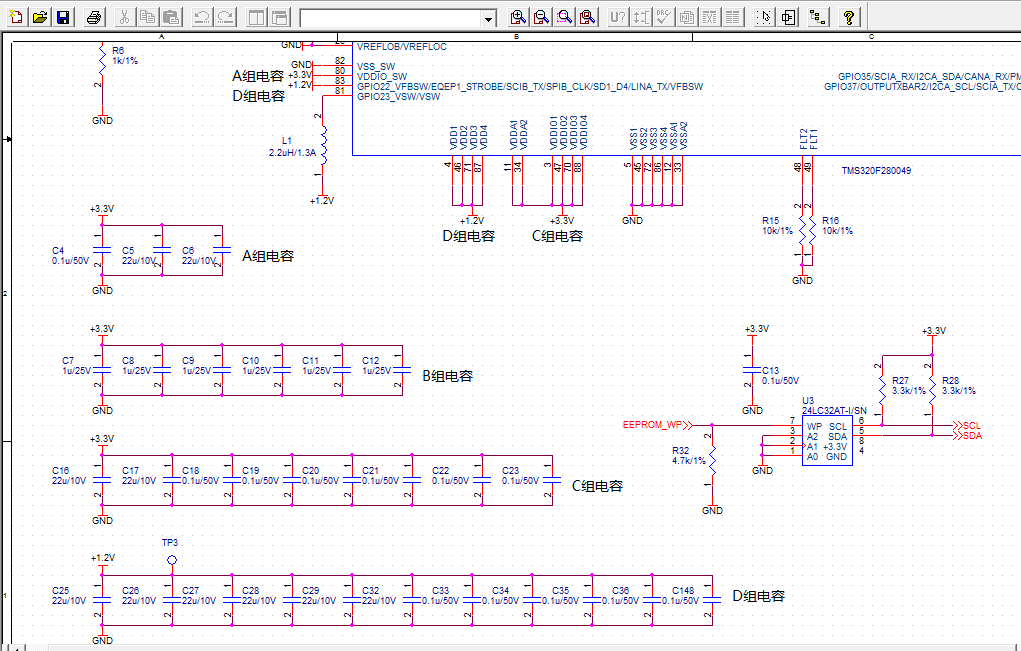

我司使用DSP280049的样机已经处于调试过程中,目前在内部1.2VDC-DC模块的使用上出现一点问题,需要各位帮忙解答一下。

测试中我们发现GPIO23_VSW输出的PWM波形并不是连续的,出现断续的情况,导致1.2V纹波较大,外部电感和电容选择的是推荐的参数。

请问出现断续现象是正常的么?或者是由于软硬件配置不对引起的该现象?麻烦指导解答,谢谢!

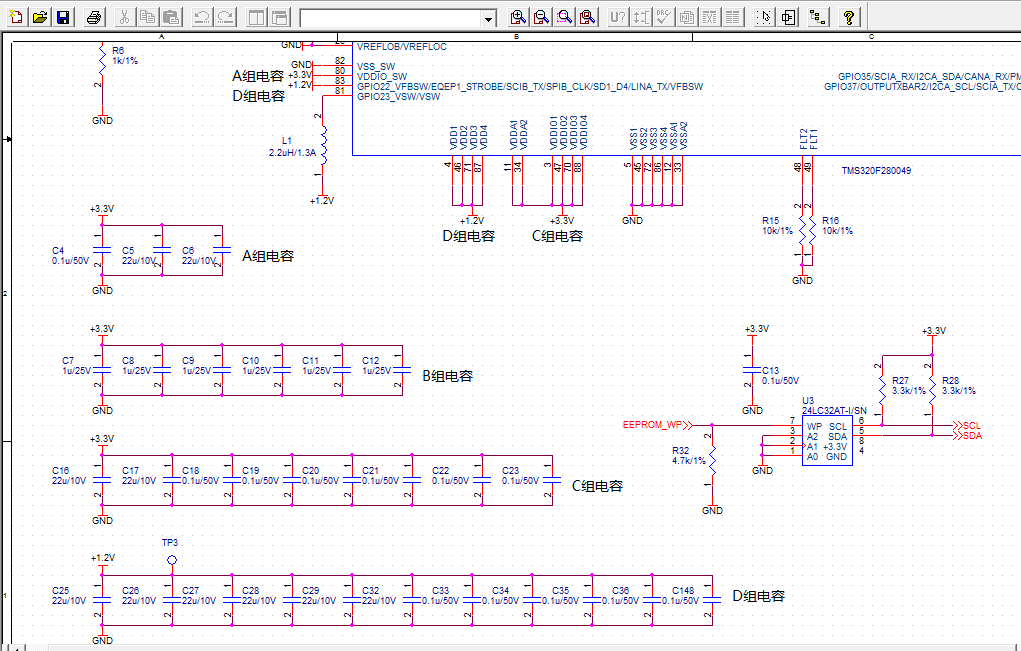

下面为与此相关的软硬件配置及波形,供参考。

软件配置:

void InitDCDC(void)

{

EALLOW;

AnalogSubsysRegs.DCDCCTL.bit.DCDCEN = 1;

While((AnalogSubsysRegs.DCDCSTS.bit.INDDETECT != 1)||(AnalogSubsysRegs.DCDCSTS.bit.SWSEQDONE!=1 ))

{//等待置位

}

EDIS;

DELAY_US(80);//延时80us

}

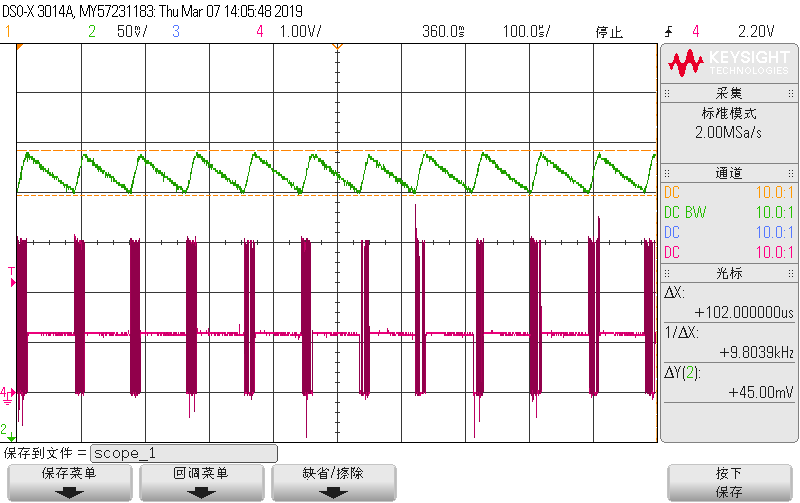

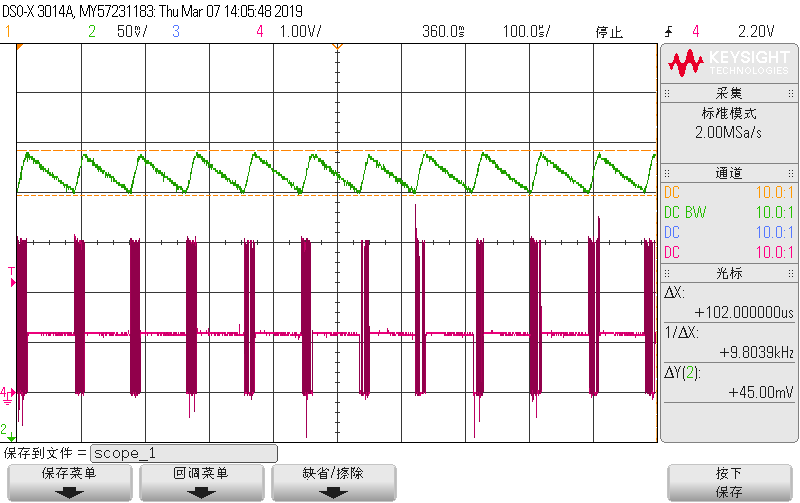

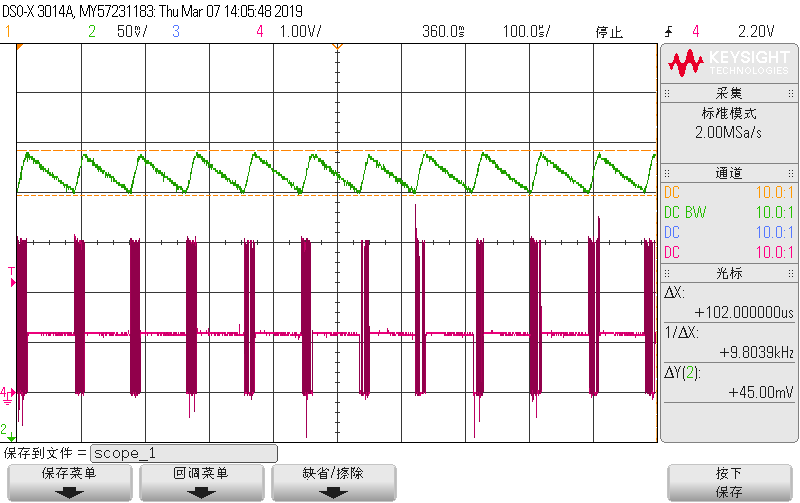

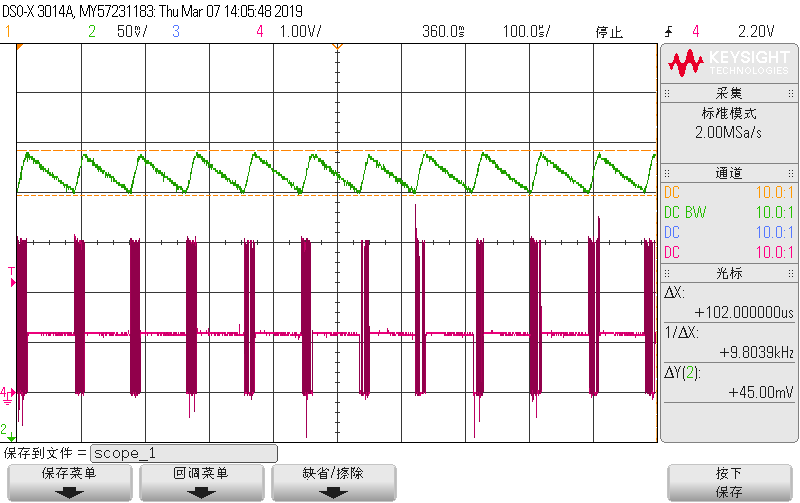

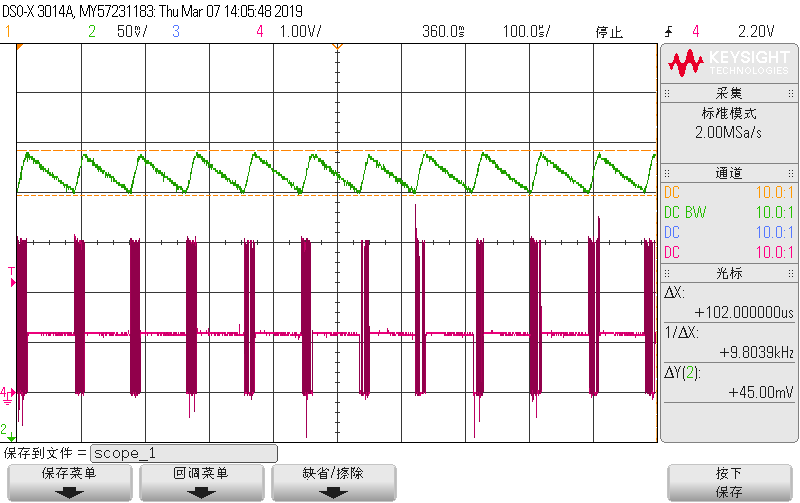

下图为我们示波器检测到的GPIO23_VSW的输出和1.2V的波形,其中红色为GPIO23_VSW的输出、绿色为1.2V波形 。

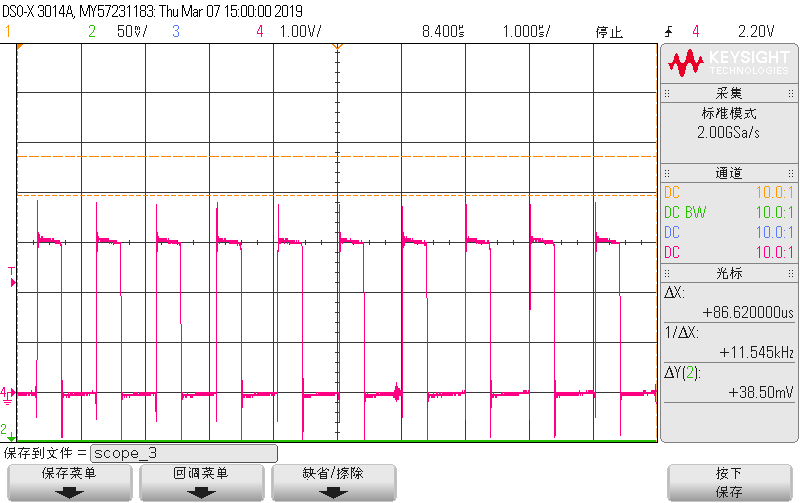

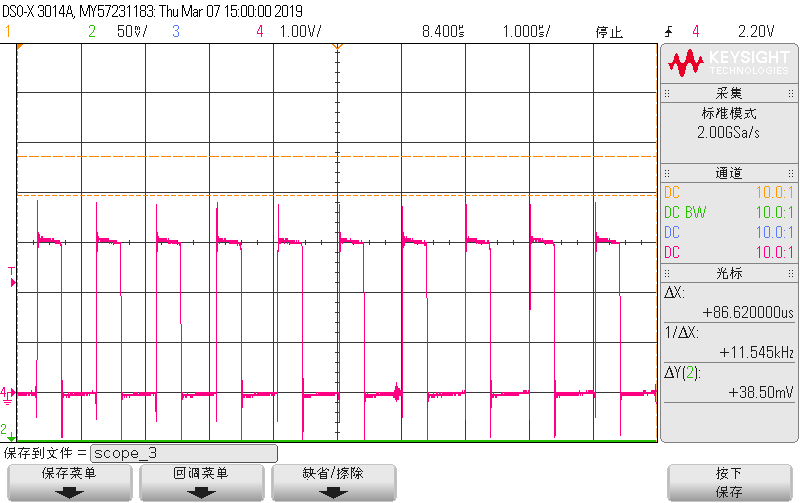

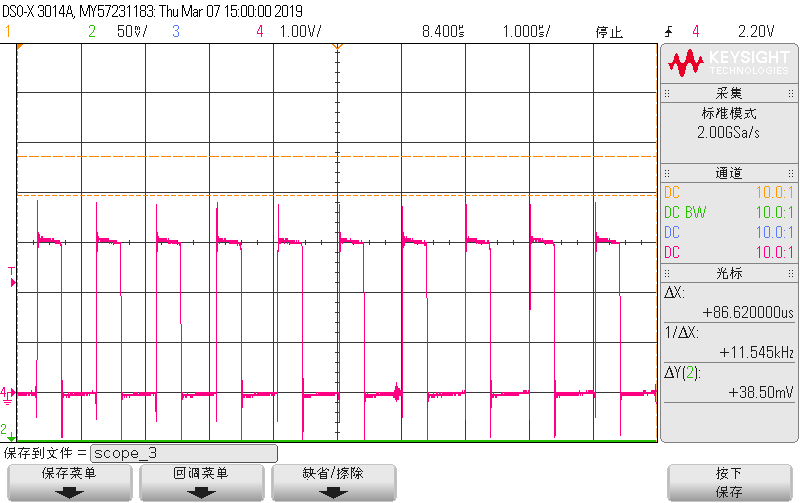

下图为展开后的有脉冲GPIO23_VSW的输出。

MING YIN:TI的各位工程师,请问有谁能帮忙解答下么?

各位资深工程师,大家好!

我司使用DSP280049的样机已经处于调试过程中,目前在内部1.2VDC-DC模块的使用上出现一点问题,需要各位帮忙解答一下。

测试中我们发现GPIO23_VSW输出的PWM波形并不是连续的,出现断续的情况,导致1.2V纹波较大,外部电感和电容选择的是推荐的参数。

请问出现断续现象是正常的么?或者是由于软硬件配置不对引起的该现象?麻烦指导解答,谢谢!

下面为与此相关的软硬件配置及波形,供参考。

软件配置:

void InitDCDC(void)

{

EALLOW;

AnalogSubsysRegs.DCDCCTL.bit.DCDCEN = 1;

While((AnalogSubsysRegs.DCDCSTS.bit.INDDETECT != 1)||(AnalogSubsysRegs.DCDCSTS.bit.SWSEQDONE!=1 ))

{//等待置位

}

EDIS;

DELAY_US(80);//延时80us

}

下图为我们示波器检测到的GPIO23_VSW的输出和1.2V的波形,其中红色为GPIO23_VSW的输出、绿色为1.2V波形 。

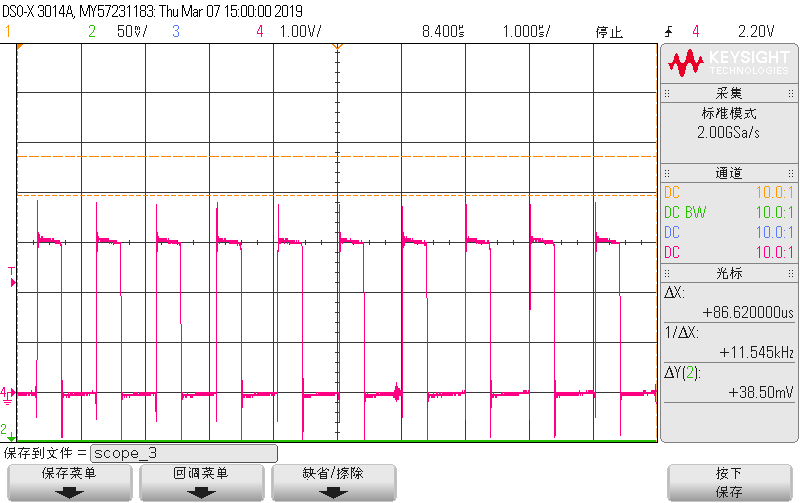

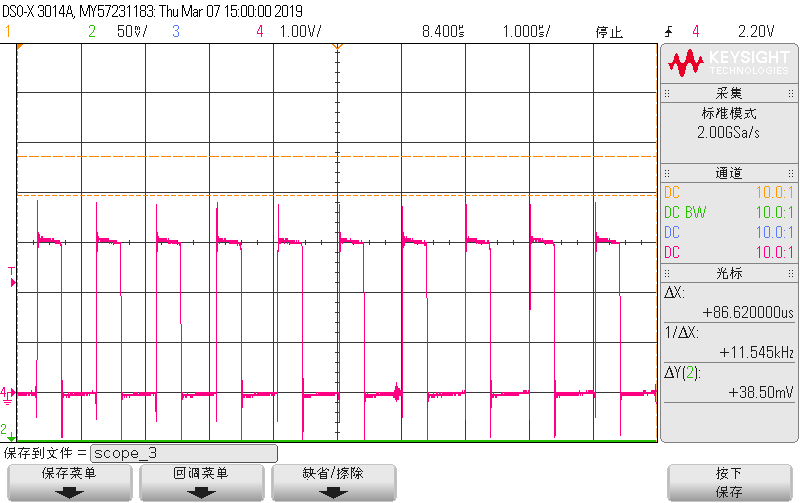

下图为展开后的有脉冲GPIO23_VSW的输出。

mangui zhang:电源文波很严重方波的过冲也很大建议加大电容试试

还有就是板卡设计电源处理这些都比较关键

各位资深工程师,大家好!

我司使用DSP280049的样机已经处于调试过程中,目前在内部1.2VDC-DC模块的使用上出现一点问题,需要各位帮忙解答一下。

测试中我们发现GPIO23_VSW输出的PWM波形并不是连续的,出现断续的情况,导致1.2V纹波较大,外部电感和电容选择的是推荐的参数。

请问出现断续现象是正常的么?或者是由于软硬件配置不对引起的该现象?麻烦指导解答,谢谢!

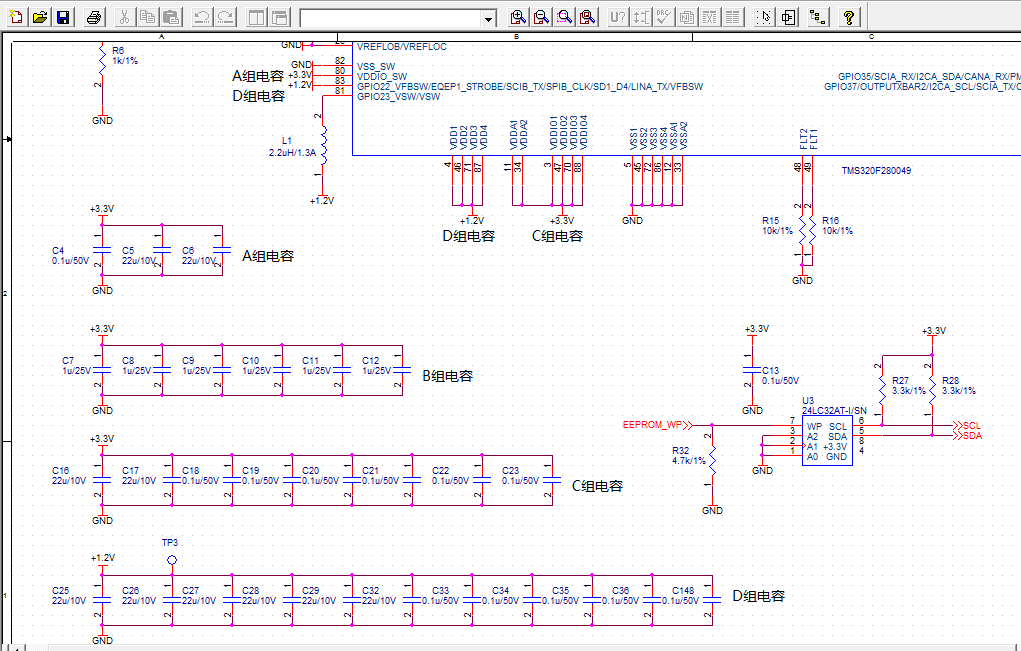

下面为与此相关的软硬件配置及波形,供参考。

软件配置:

void InitDCDC(void)

{

EALLOW;

AnalogSubsysRegs.DCDCCTL.bit.DCDCEN = 1;

While((AnalogSubsysRegs.DCDCSTS.bit.INDDETECT != 1)||(AnalogSubsysRegs.DCDCSTS.bit.SWSEQDONE!=1 ))

{//等待置位

}

EDIS;

DELAY_US(80);//延时80us

}

下图为我们示波器检测到的GPIO23_VSW的输出和1.2V的波形,其中红色为GPIO23_VSW的输出、绿色为1.2V波形 。

下图为展开后的有脉冲GPIO23_VSW的输出。

MING YIN:

回复 mangui zhang:

非常感谢您的建议,方波过冲问题可以通过加电容解决

但我们现在最关注的是GPIO23_VSW输出脉冲断续的问题,这才是导致电源纹波的根本原因

电源纹波已经超过了3%,这对于这个芯片内核的稳定性来说存在风险

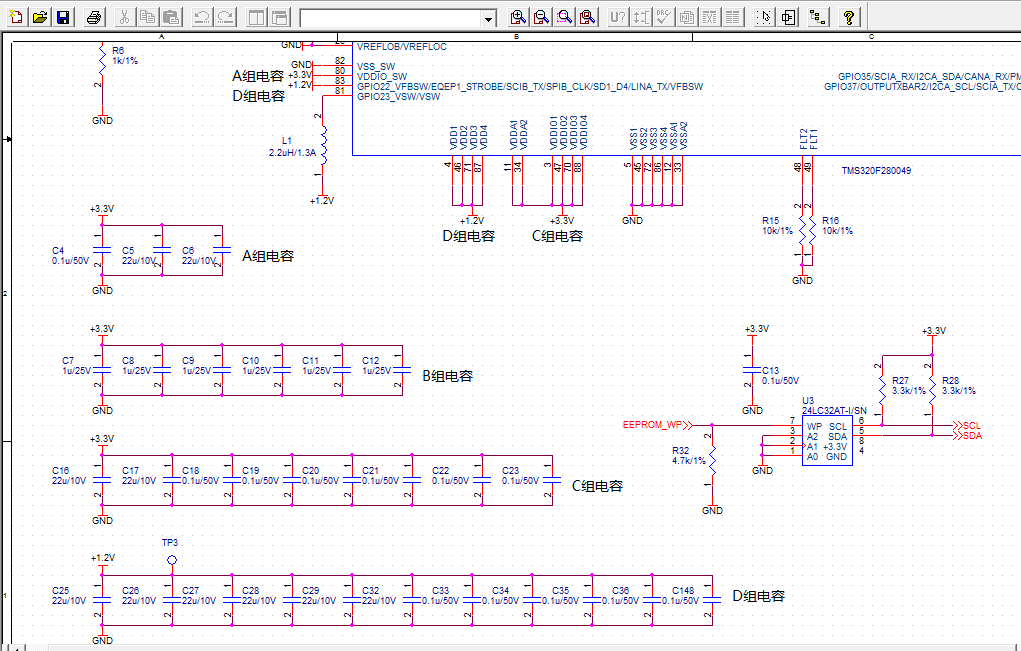

各位资深工程师,大家好!

我司使用DSP280049的样机已经处于调试过程中,目前在内部1.2VDC-DC模块的使用上出现一点问题,需要各位帮忙解答一下。

测试中我们发现GPIO23_VSW输出的PWM波形并不是连续的,出现断续的情况,导致1.2V纹波较大,外部电感和电容选择的是推荐的参数。

请问出现断续现象是正常的么?或者是由于软硬件配置不对引起的该现象?麻烦指导解答,谢谢!

下面为与此相关的软硬件配置及波形,供参考。

软件配置:

void InitDCDC(void)

{

EALLOW;

AnalogSubsysRegs.DCDCCTL.bit.DCDCEN = 1;

While((AnalogSubsysRegs.DCDCSTS.bit.INDDETECT != 1)||(AnalogSubsysRegs.DCDCSTS.bit.SWSEQDONE!=1 ))

{//等待置位

}

EDIS;

DELAY_US(80);//延时80us

}

下图为我们示波器检测到的GPIO23_VSW的输出和1.2V的波形,其中红色为GPIO23_VSW的输出、绿色为1.2V波形 。

下图为展开后的有脉冲GPIO23_VSW的输出。

Green Deng:你好,首先说明一下本人还没有使用过这块芯片,所以不确定提到的内容是否关联,如果有不对的地方还请告知。

1、根据芯片数据手册描述,TI是不推荐使用GPIO23_VSW作为通用输入输出口的。

This pin is configured for DC-DC mode by default. If the internal DC-DC regulator is not used, this can be configured as General-Purpose Input Output 23 by disabling DC-DC and clearing their bits in GPAAMSEL register. This pin has an internal capacitance of approximately 100 pF. TI Recommends using an alternate GPIO, or using this pin only for applications which do not require a fast switching response.

2、在芯片datasheet第65页的5.9.1.2.1 PCB Layout and Component Guidelines中有提到很多layout的指导不知道你这边是否有按照上面说的做?

各位资深工程师,大家好!

我司使用DSP280049的样机已经处于调试过程中,目前在内部1.2VDC-DC模块的使用上出现一点问题,需要各位帮忙解答一下。

测试中我们发现GPIO23_VSW输出的PWM波形并不是连续的,出现断续的情况,导致1.2V纹波较大,外部电感和电容选择的是推荐的参数。

请问出现断续现象是正常的么?或者是由于软硬件配置不对引起的该现象?麻烦指导解答,谢谢!

下面为与此相关的软硬件配置及波形,供参考。

软件配置:

void InitDCDC(void)

{

EALLOW;

AnalogSubsysRegs.DCDCCTL.bit.DCDCEN = 1;

While((AnalogSubsysRegs.DCDCSTS.bit.INDDETECT != 1)||(AnalogSubsysRegs.DCDCSTS.bit.SWSEQDONE!=1 ))

{//等待置位

}

EDIS;

DELAY_US(80);//延时80us

}

下图为我们示波器检测到的GPIO23_VSW的输出和1.2V的波形,其中红色为GPIO23_VSW的输出、绿色为1.2V波形 。

下图为展开后的有脉冲GPIO23_VSW的输出。

MING YIN:

回复 Green Deng:

您好,感谢您的回复

1、我们并没有把GPIO23_VSW作为通用输入输出口,而是其默认状态

2、layout有严格参考指导的说明

TI中文支持网

TI中文支持网