1使用的芯片:28335

2使用的模块:epwm,ADC

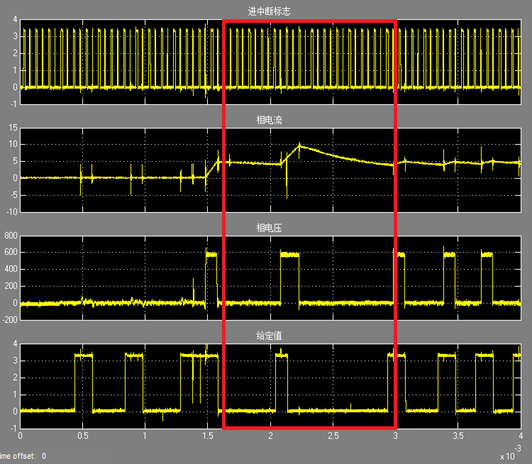

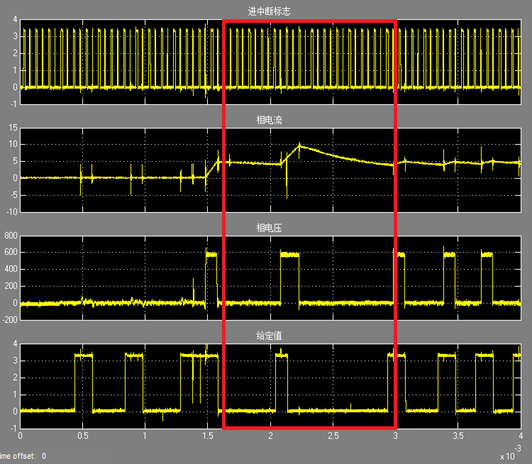

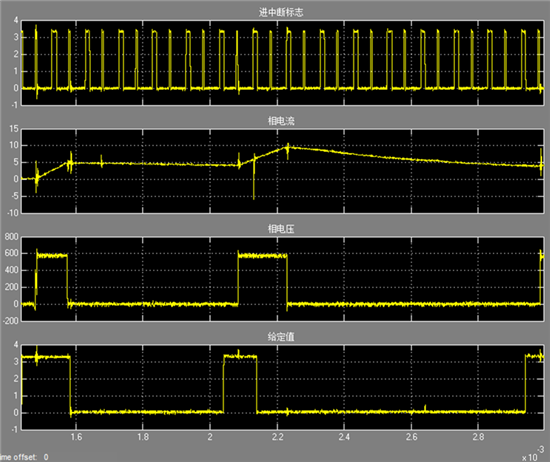

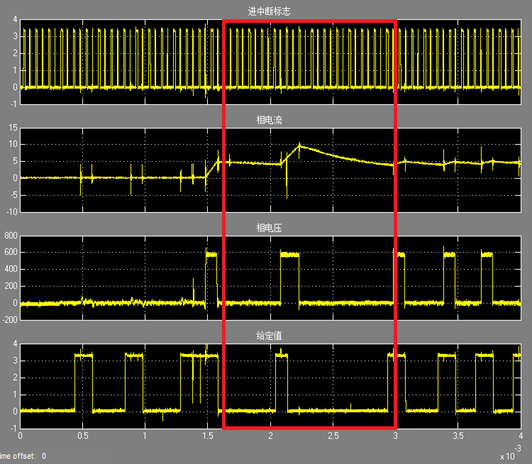

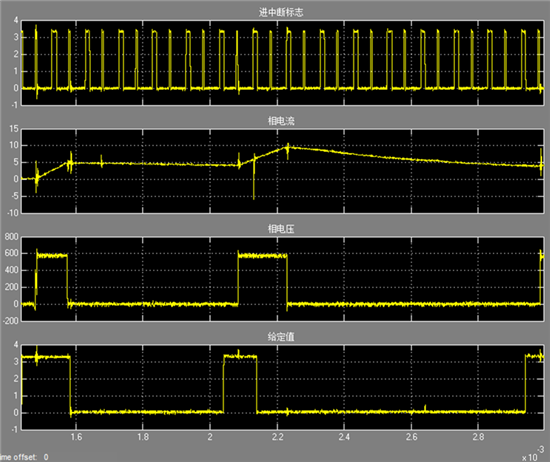

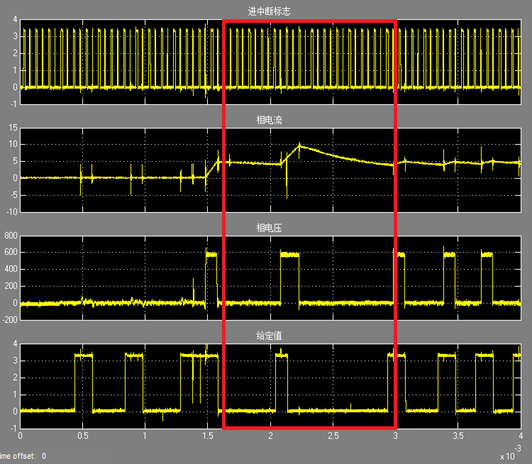

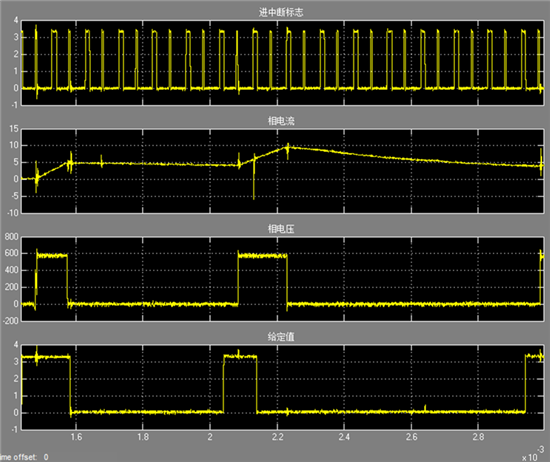

3应用背景:用于电流斩波控制,epwm采用上下计数方式,产生两个中断,如进中断标志中的下溢中断(较窄者)和上溢中断(较宽者),两个中断内的程序有些差别,但都做了电流ADC采样,原理上相电压应当在给定置零时就关断,但如红框放大区域,从电流毛刺上看出电流ADC采样已经进行,但在宽脉冲时装载失败,但是后面部分却又可以装载成功了,仅在前两个给定值跳变时出现可能的装载失败。两个中断分别采用的零位置装载和周期值装载。

已经尝试过更改装载方式和比较值避免写0和满值(0~10000,写10和9990),均没有效果。

放大

Eason Wang:

28335 属于是C2000的芯片

1使用的芯片:28335

2使用的模块:epwm,ADC

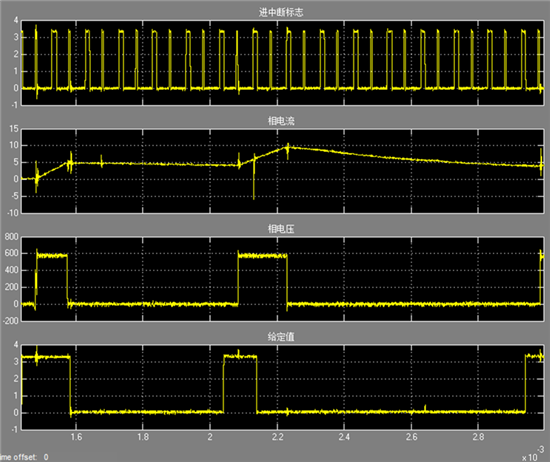

3应用背景:用于电流斩波控制,epwm采用上下计数方式,产生两个中断,如进中断标志中的下溢中断(较窄者)和上溢中断(较宽者),两个中断内的程序有些差别,但都做了电流ADC采样,原理上相电压应当在给定置零时就关断,但如红框放大区域,从电流毛刺上看出电流ADC采样已经进行,但在宽脉冲时装载失败,但是后面部分却又可以装载成功了,仅在前两个给定值跳变时出现可能的装载失败。两个中断分别采用的零位置装载和周期值装载。

已经尝试过更改装载方式和比较值避免写0和满值(0~10000,写10和9990),均没有效果。

放大

Shuchun Yao:

回复 Eason Wang:

谢谢,我转到另一边又发了一遍了

1使用的芯片:28335

2使用的模块:epwm,ADC

3应用背景:用于电流斩波控制,epwm采用上下计数方式,产生两个中断,如进中断标志中的下溢中断(较窄者)和上溢中断(较宽者),两个中断内的程序有些差别,但都做了电流ADC采样,原理上相电压应当在给定置零时就关断,但如红框放大区域,从电流毛刺上看出电流ADC采样已经进行,但在宽脉冲时装载失败,但是后面部分却又可以装载成功了,仅在前两个给定值跳变时出现可能的装载失败。两个中断分别采用的零位置装载和周期值装载。

已经尝试过更改装载方式和比较值避免写0和满值(0~10000,写10和9990),均没有效果。

放大

rookiecalf:

回复 Shuchun Yao:

你说的关断是通过什么方式关断的,是通过配置强制给定电平,还是算法运算后出cmpr值,如果是运算考虑是否运算有什么BUG

1使用的芯片:28335

2使用的模块:epwm,ADC

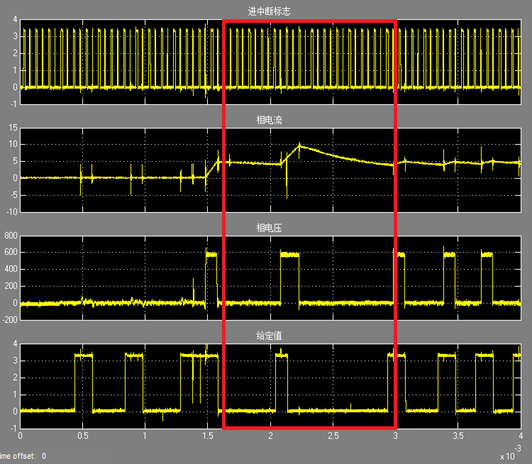

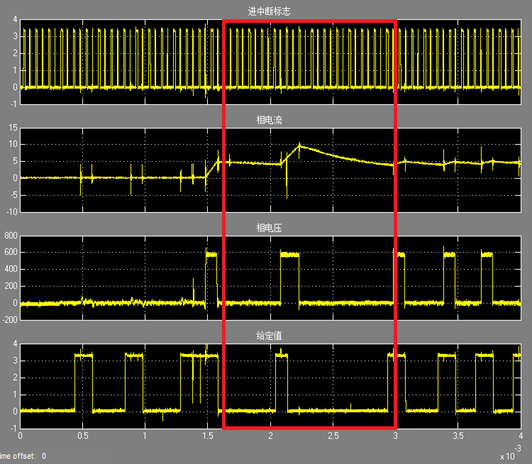

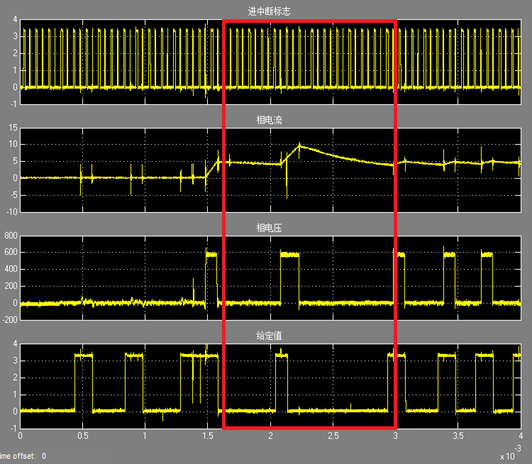

3应用背景:用于电流斩波控制,epwm采用上下计数方式,产生两个中断,如进中断标志中的下溢中断(较窄者)和上溢中断(较宽者),两个中断内的程序有些差别,但都做了电流ADC采样,原理上相电压应当在给定置零时就关断,但如红框放大区域,从电流毛刺上看出电流ADC采样已经进行,但在宽脉冲时装载失败,但是后面部分却又可以装载成功了,仅在前两个给定值跳变时出现可能的装载失败。两个中断分别采用的零位置装载和周期值装载。

已经尝试过更改装载方式和比较值避免写0和满值(0~10000,写10和9990),均没有效果。

放大

Shuchun Yao:

回复 rookiecalf:

是有通过ADC采样值通过计算比较后的。问题是从现象中看只有在前两个电流尖峰的区域内会出现类似与装载不上的问题,而后面的就没有出现装载不上的问题

1使用的芯片:28335

2使用的模块:epwm,ADC

3应用背景:用于电流斩波控制,epwm采用上下计数方式,产生两个中断,如进中断标志中的下溢中断(较窄者)和上溢中断(较宽者),两个中断内的程序有些差别,但都做了电流ADC采样,原理上相电压应当在给定置零时就关断,但如红框放大区域,从电流毛刺上看出电流ADC采样已经进行,但在宽脉冲时装载失败,但是后面部分却又可以装载成功了,仅在前两个给定值跳变时出现可能的装载失败。两个中断分别采用的零位置装载和周期值装载。

已经尝试过更改装载方式和比较值避免写0和满值(0~10000,写10和9990),均没有效果。

放大

囧:

回复 Shuchun Yao:

你的EPWM初始化代码能贴出来看一下吗?

1使用的芯片:28335

2使用的模块:epwm,ADC

3应用背景:用于电流斩波控制,epwm采用上下计数方式,产生两个中断,如进中断标志中的下溢中断(较窄者)和上溢中断(较宽者),两个中断内的程序有些差别,但都做了电流ADC采样,原理上相电压应当在给定置零时就关断,但如红框放大区域,从电流毛刺上看出电流ADC采样已经进行,但在宽脉冲时装载失败,但是后面部分却又可以装载成功了,仅在前两个给定值跳变时出现可能的装载失败。两个中断分别采用的零位置装载和周期值装载。

已经尝试过更改装载方式和比较值避免写0和满值(0~10000,写10和9990),均没有效果。

放大

Shuchun Yao:

回复 囧:

初始化部分:

#define PWM_INIT_MACRO(v) \ /* Setup Sync*/ \ EPwm1Regs.TBCTL.bit.SYNCOSEL = 0; /* Pass through*/ \ EPwm2Regs.TBCTL.bit.SYNCOSEL = 0; /* Pass through*/ \ EPwm3Regs.TBCTL.bit.SYNCOSEL = 0; /* Pass through*/ \ \ /* Allow each timer to be sync'ed*/ \ EPwm1Regs.TBCTL.bit.PHSEN = 1; \ EPwm2Regs.TBCTL.bit.PHSEN = 1; \ EPwm3Regs.TBCTL.bit.PHSEN = 1; \ \ /* Init Timer-Base Period Register for EPWM1-EPWM3*/ \ EPwm1Regs.TBPRD = v.PeriodMax; \ EPwm2Regs.TBPRD = v.PeriodMax; \ EPwm3Regs.TBPRD = v.PeriodMax; \ \ /* Init Timer-Base Phase Register for EPWM1-EPWM3*/ \ EPwm1Regs.TBPHS.half.TBPHS = 0; \ EPwm2Regs.TBPHS.half.TBPHS = 0; \ EPwm3Regs.TBPHS.half.TBPHS = 0; \ \ /* Init Timer-Base Control Register for EPWM1-EPWM3*/ \ EPwm1Regs.TBCTL.all = PWM_INIT_STATE; \ EPwm2Regs.TBCTL.all = PWM_INIT_STATE; \ EPwm3Regs.TBCTL.all = PWM_INIT_STATE; \ /* Init Compare Control Register for EPWM1-EPWM3*/ \ EPwm1Regs.CMPCTL.all = CMPCTL_INIT_STATE; \ EPwm2Regs.CMPCTL.all = CMPCTL_INIT_STATE; \ EPwm3Regs.CMPCTL.all = CMPCTL_INIT_STATE; \ /* EPWM1-EPWM3 的上下桥分别动作于CMPA、CMPB增计数时,高有效*/ \ EPwm1Regs.AQCTLA.all = AQCTLA_INIT_STATE; \ EPwm1Regs.AQCTLB.all = AQCTLB_INIT_STATE; \ EPwm2Regs.AQCTLA.all = AQCTLA_INIT_STATE; \ EPwm2Regs.AQCTLB.all = AQCTLB_INIT_STATE; \ EPwm3Regs.AQCTLA.all = AQCTLA_INIT_STATE; \ EPwm3Regs.AQCTLB.all = AQCTLB_INIT_STATE; \ /* 禁止死区*/ \ EPwm1Regs.DBCTL.all = DBCTL_INIT_STATE; \ EPwm2Regs.DBCTL.all = DBCTL_INIT_STATE; \ EPwm3Regs.DBCTL.all = DBCTL_INIT_STATE; \ /* Init Dead-Band Generator for EPWM1-EPWM3*/ \ EPwm1Regs.DBFED = DBCNT_INIT_STATE; \ EPwm1Regs.DBRED = DBCNT_INIT_STATE; \ EPwm2Regs.DBFED = DBCNT_INIT_STATE; \ EPwm2Regs.DBRED = DBCNT_INIT_STATE; \ EPwm3Regs.DBFED = DBCNT_INIT_STATE; \ EPwm3Regs.DBRED = DBCNT_INIT_STATE; \ /* Init PWM Chopper Control Register for EPWM1-EPWM3*/ \ EPwm1Regs.PCCTL.all = PCCTL_INIT_STATE; \ EPwm2Regs.PCCTL.all = PCCTL_INIT_STATE; \ EPwm3Regs.PCCTL.all = PCCTL_INIT_STATE; \ EALLOW; /* Enable EALLOW */ \ \ /* Init Trip Zone Select Register*/ \ EPwm1Regs.TZSEL.all = TZSEL_INIT_STATE; \ EPwm2Regs.TZSEL.all = TZSEL_INIT_STATE; \ EPwm3Regs.TZSEL.all = TZSEL_INIT_STATE; \ /* Init Trip Zone Control Register*/ \/* EPwm1Regs.TZCTL.all = TZCTL_INIT_STATE; \ EPwm2Regs.TZCTL.all = TZCTL_INIT_STATE; \ EPwm3Regs.TZCTL.all = TZCTL_INIT_STATE; \*/ \ EDIS; /* Disable EALLOW*/ \ EPwm1Regs.CMPA.half.CMPA = v.PeriodMax; \ EPwm1Regs.CMPB = v.PeriodMax; \ EPwm2Regs.CMPA.half.CMPA = v.PeriodMax; \ EPwm2Regs.CMPB = v.PeriodMax; \ EPwm3Regs.CMPA.half.CMPA = v.PeriodMax; \ EPwm3Regs.CMPB = v.PeriodMax;

中断使能部分

// Enable CNT_zero interrupt using EPWM1 Time-base EPwm1Regs.ETSEL.bit.INTEN = 1; // Enable EPWM1INT generation EPwm1Regs.ETSEL.bit.INTSEL = 1; // Enable interrupt CNT_zero event EPwm1Regs.ETPS.bit.INTPRD = 1; // Generate interrupt on the 1st event EPwm1Regs.ETCLR.bit.INT = 1; // Enable more interrupts

// Enable CNT_period interrupt using EPWM2 Time-base EPwm2Regs.ETSEL.bit.INTEN = 1; // Enable EPWM2INT generation EPwm2Regs.ETSEL.bit.INTSEL = 2; // Enable interrupt CNT_period event EPwm2Regs.ETPS.bit.INTPRD = 1; // Generate interrupt on the 1st event EPwm2Regs.ETCLR.bit.INT = 1; // Enable more interrupts

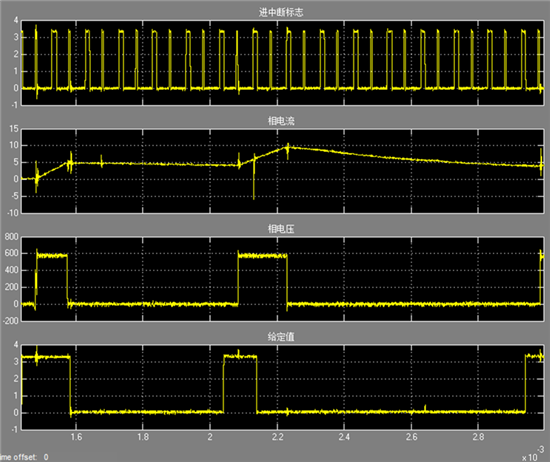

1使用的芯片:28335

2使用的模块:epwm,ADC

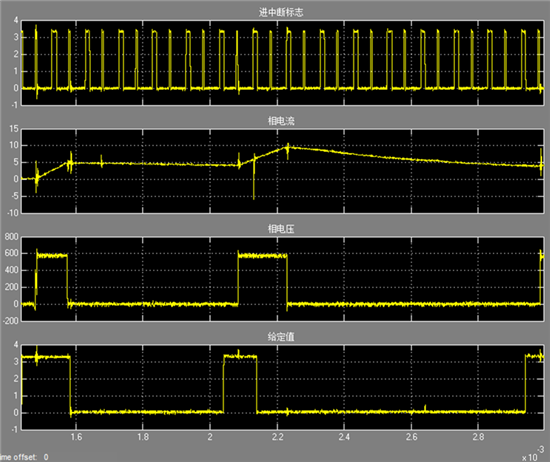

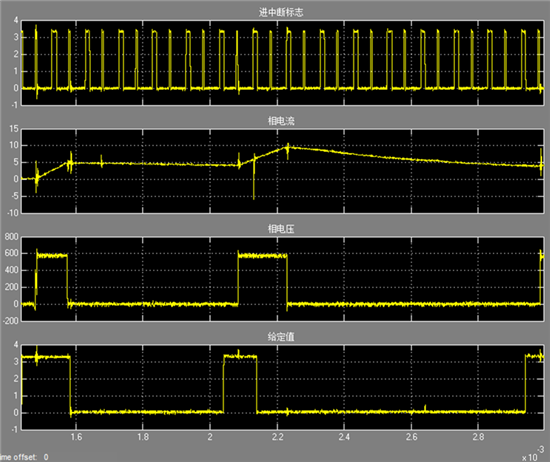

3应用背景:用于电流斩波控制,epwm采用上下计数方式,产生两个中断,如进中断标志中的下溢中断(较窄者)和上溢中断(较宽者),两个中断内的程序有些差别,但都做了电流ADC采样,原理上相电压应当在给定置零时就关断,但如红框放大区域,从电流毛刺上看出电流ADC采样已经进行,但在宽脉冲时装载失败,但是后面部分却又可以装载成功了,仅在前两个给定值跳变时出现可能的装载失败。两个中断分别采用的零位置装载和周期值装载。

已经尝试过更改装载方式和比较值避免写0和满值(0~10000,写10和9990),均没有效果。

放大

囧:

回复 Shuchun Yao:

EPwm1Regs.TBCTL.bit.PHSEN = 1; \EPwm2Regs.TBCTL.bit.PHSEN = 1; \EPwm3Regs.TBCTL.bit.PHSEN = 1; \ 建议关掉PWM1的同步功能,如果PWM1不接受外部同步的话,否则容易在0点被干扰。

TI中文支持网

TI中文支持网